Reset and clock control (RCC) RM0440

334/2126 RM0440 Rev 4

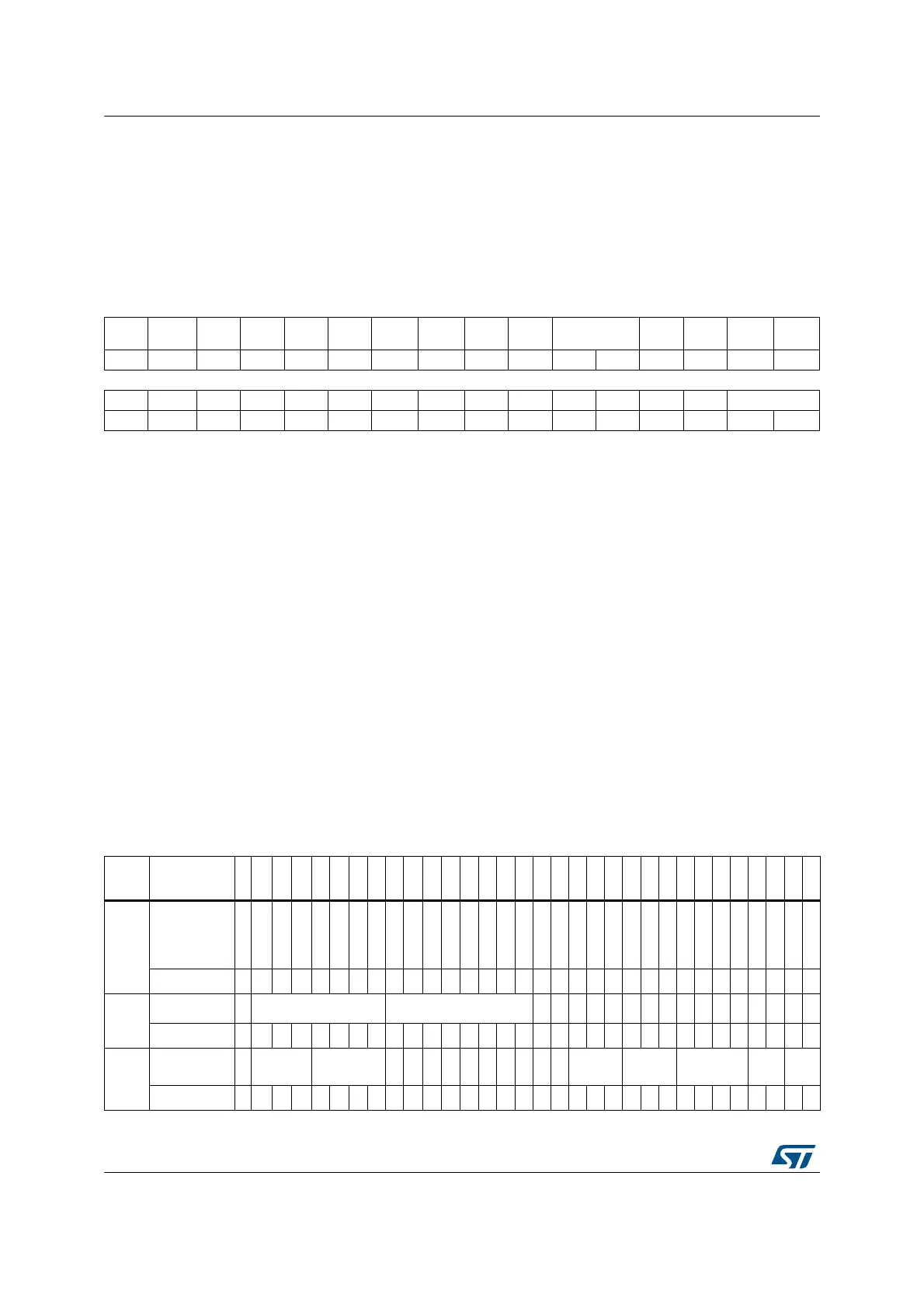

7.4.30 Peripherals independent clock configuration register (RCC_CCIPR2)

Address: 0x9C

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

Wait states are inserted in case of successive accesses to this register.

7.4.31 RCC register map

The following table gives the RCC register map and the reset values.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

QSPISEL

[1:0]

Res. Res. Res. Res.

rw rw

1514131211109 8 765432 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. I2C4SEL[1:0]

rw rw

Bits 31:22 Reserved, must be kept at reset value.

Bits 21:20 QSPISEL[1:0]: QUADSPI clock source selection

Set and reset by software.

00: system clock selected as QUADSPI kernel clock

01: HSI16 clock selected as QUADSPI kernel clock

10: PLL “Q” clock selected as QUADSPI kernel clock

11: reserved

Bits 19:2 Reserved, must be kept at reset value.

Bits 1:0 I2C4SEL[1:0]: I2C4 clock source selection

These bits are set and cleared by software to select the I2C4 clock source.

00: PCLK selected as I2C4 clock

01: System clock (SYSCLK) selected as I2C4 clock

10: HSI16 clock selected as I2C4 clock

11: reserved

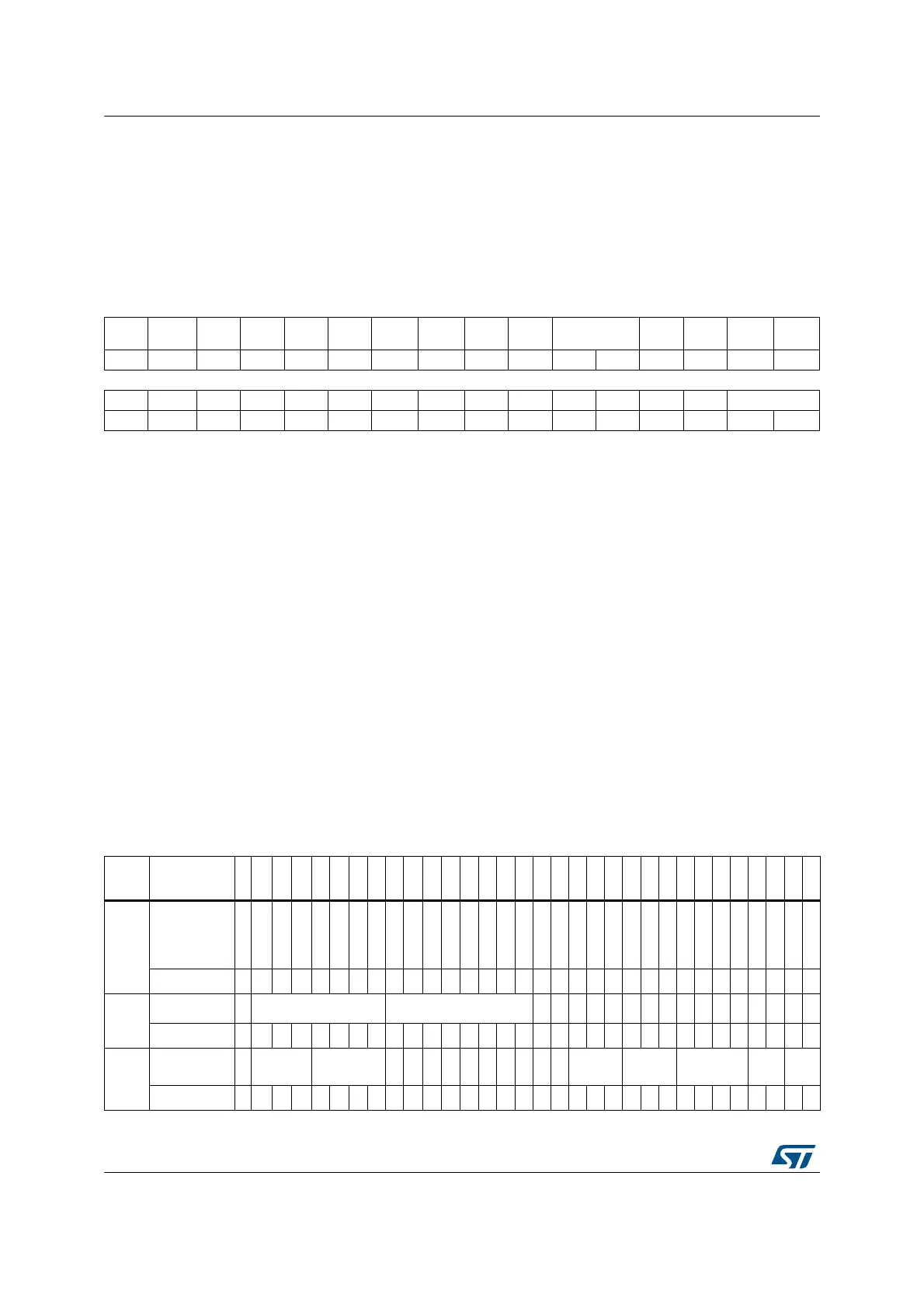

Table 51. RCC register map and reset values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x00

RCC_CR

Res.

Res.

Res.

Res.

Res.

Res.

PLLRDY

PLLON

Res.

Res.

Res.

Res.

CSSON

HSEBYP

HSERDY

HSEON

Res.

Res.

Res.

Res.

Res.

HSIRDY

HSIKERON

HSION

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Reset value

0 00000 0000 000

0x04

RCC_ICSCR

Res.

HSITRIM[6:0] HSICAL[7:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Reset value

1 0 0 0 0 0 0XXXXXXXX

0x08

RCC_CFGR

Res.

MCOPRE

[2:0]

MCOSEL

[3:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PPRE2

[2:0]

PPRE1

[2:0]

HPRE[3:0]

SWS

[1:0]

SW

[1:0]

Reset value

0 0 00000 00000000000000

Loading...

Loading...