148

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Peripheral Information and Electrical Specifications Copyright © 2009–2017, Texas Instruments Incorporated

(1) ACLKX0 internal – McASP0 ACLKXCTL.CLKXM = 1, PDIR.ACLKX = 1

ACLKX0 external input – McASP0 ACLKXCTL.CLKXM = 0, PDIR.ACLKX = 0

ACLKX0 external output – McASP0 ACLKXCTL.CLKXM = 0, PDIR.ACLKX = 1

ACLKR0 internal – McASP0 ACLKRCTL.CLKRM = 1, PDIR.ACLKR =1

ACLKR0 external input – McASP0 ACLKRCTL.CLKRM = 0, PDIR.ACLKR = 0

ACLKR0 external output – McASP0 ACLKRCTL.CLKRM = 0, PDIR.ACLKR = 1

(2) P = SYSCLK2 period

(3) This timing is limited by the timing shown or 2P, whichever is greater.

(4) McASP0 ACLKXCTL.ASYNC=1: Receiver is clocked by its own ACLKR0

(5) McASP0 ACLKXCTL.ASYNC=0: Receiver is clocked by transmitter's ACLKX0

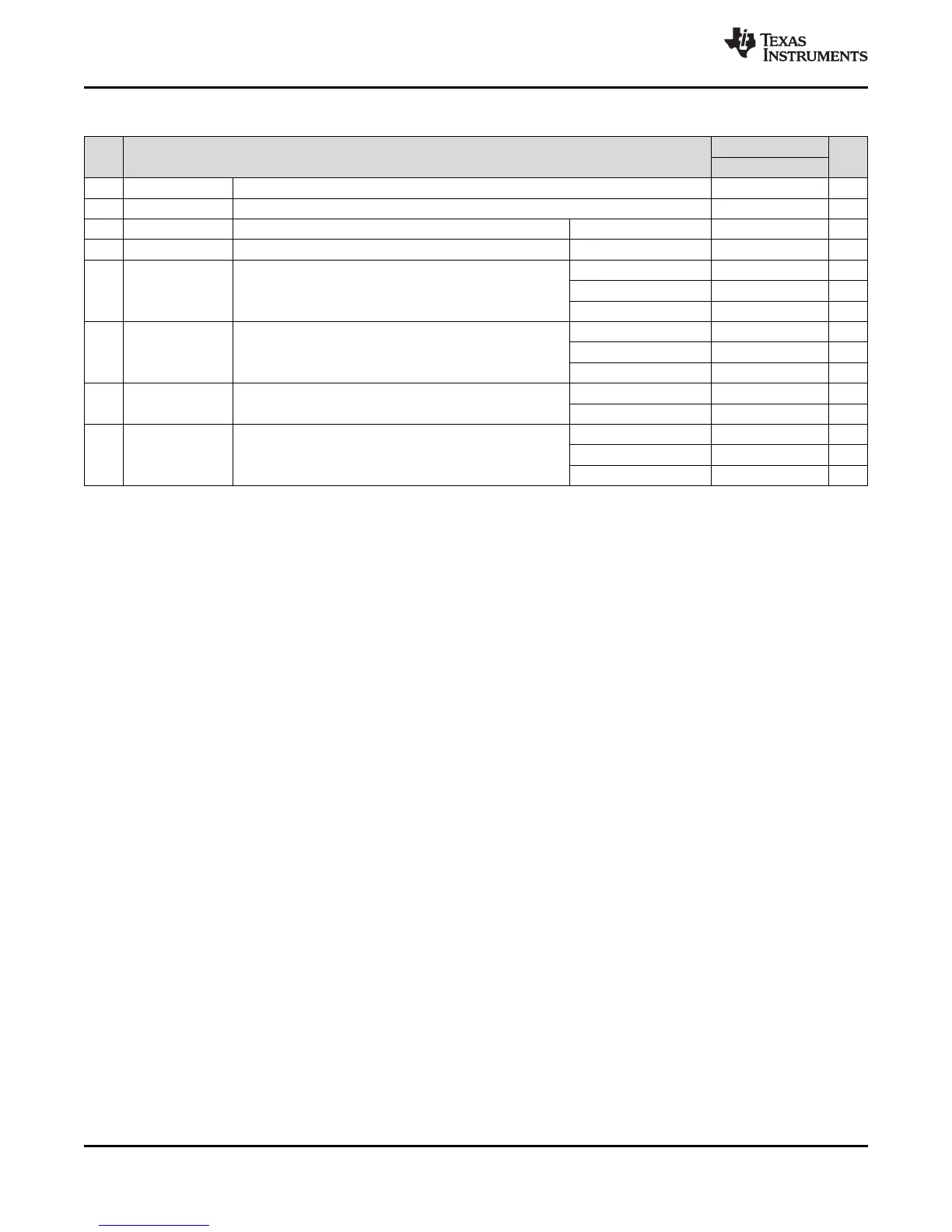

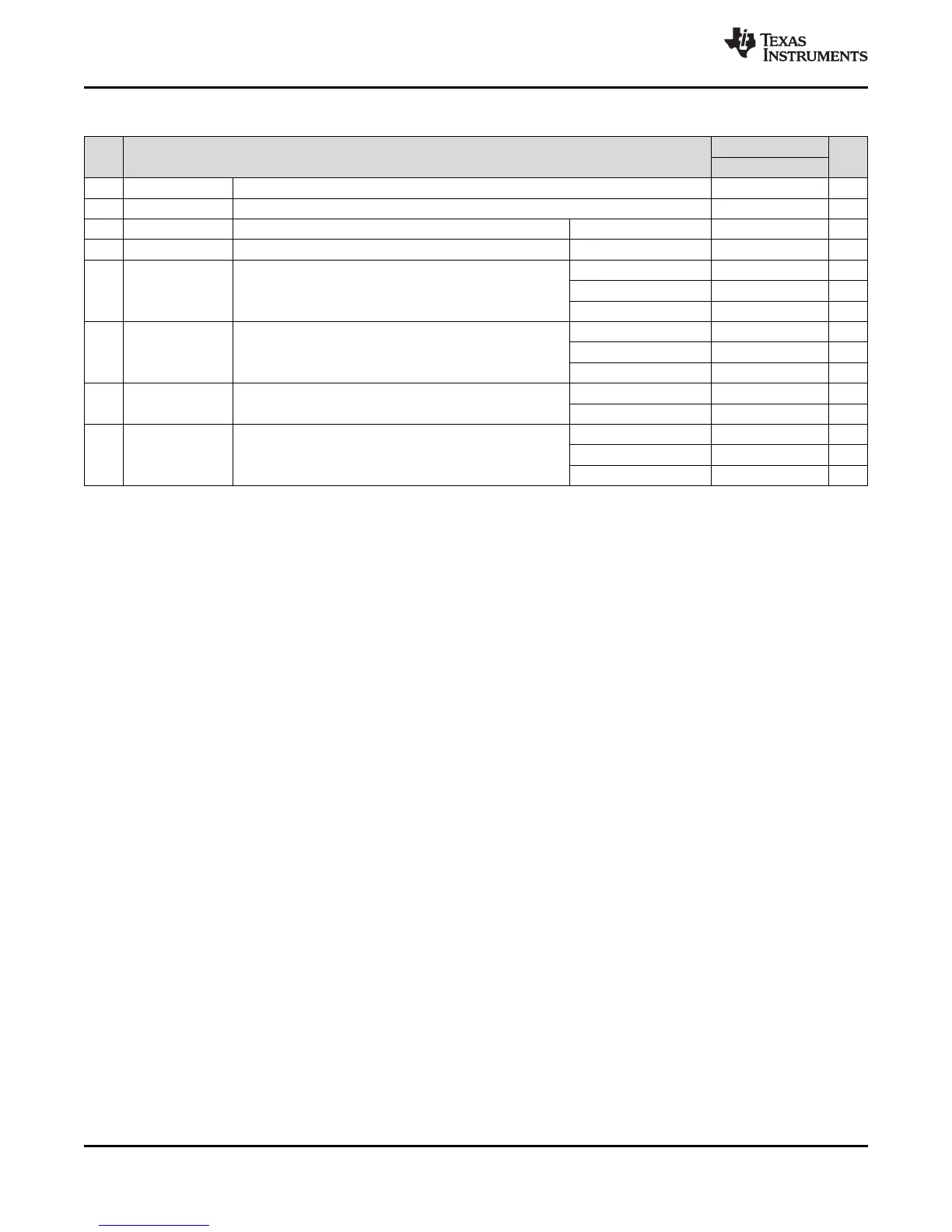

Table 6-53. Timing Requirements for McASP0 (1.0V)

(1)(2)

NO.

1.0V

UNIT

MIN MAX

1 t

c(AHCLKRX)

Cycle time, AHCLKR/X 35 ns

2 t

w(AHCLKRX)

Pulse duration, AHCLKR/X high or low 17.5 ns

3 t

c(ACLKRX)

Cycle time, ACLKR/X AHCLKR/X ext 35

(3)

ns

4 t

w(ACLKRX)

Pulse duration, ACLKR/W high or low AHCLKR/X ext 17.5 ns

5 t

su(AFSRX-ACLKRX)

Setup time,

AFSR/X input to ACLKR/X

(4)

AHCLKR/X int 16 ns

AHCLKR/X ext input 5.5 ns

AHCLKR/X ext output 5.5 ns

6 t

h(ACLKRX-AFSRX)

Hold time,

AFSR/X input after ACLKR/X

(4)

AHCLKR/X int -2 ns

AHCLKR/X ext input 1 ns

AHCLKR/X ext output 1 ns

7 t

su(AXR-ACLKRX)

Setup time,

AXR0[n] input to ACLKR/X

(4)(5)

AHCLKR/X int 16 ns

AHCLKR/X ext 5.5 ns

8 t

h(ACLKRX-AXR)

Hold time,

AXR0[n] input after ACLKR/X

(4)(5)

AHCLKR/X int -2 ns

AHCLKR/X ext input 5 ns

AHCLKR/X ext output 5 ns

Loading...

Loading...