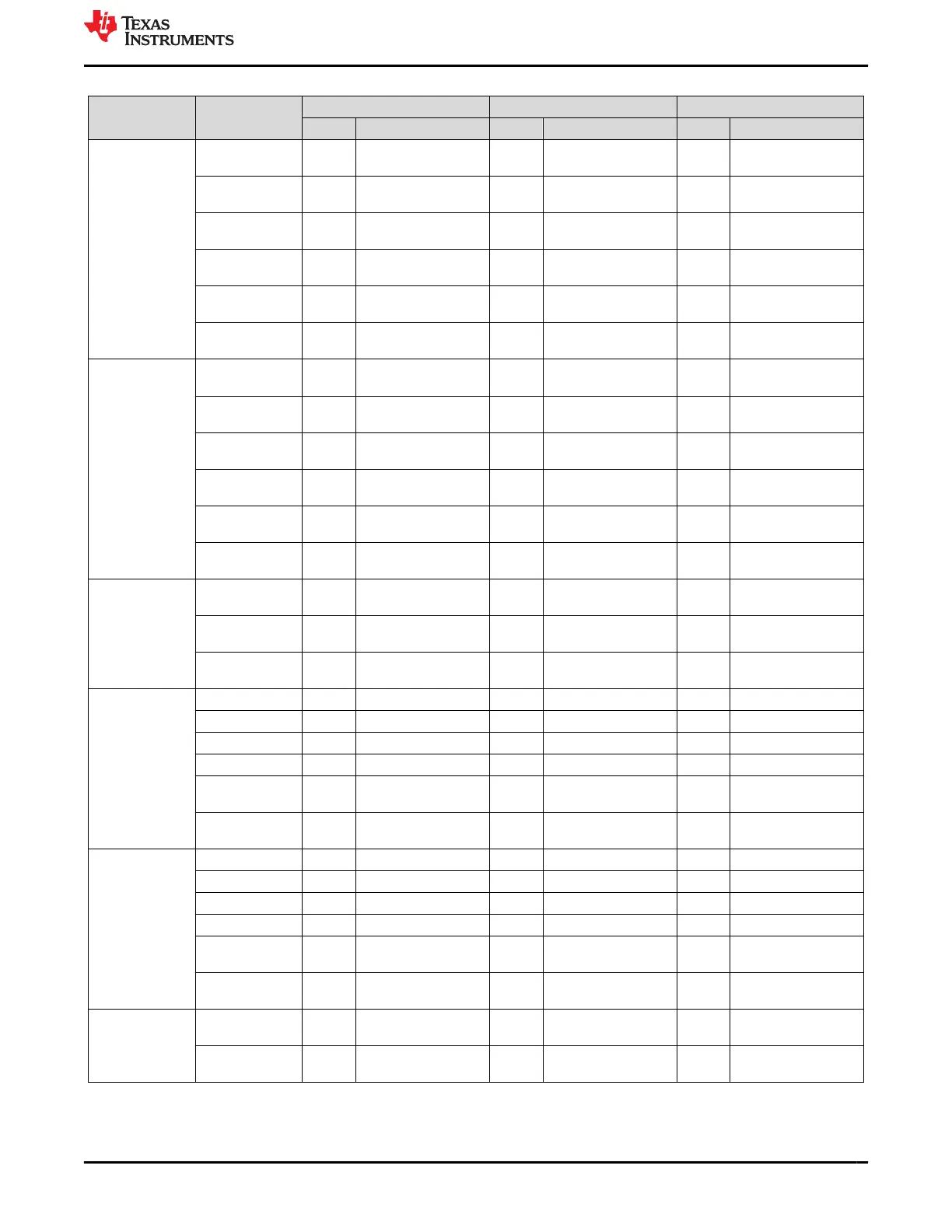

Table 5-8. Interrupt NVM Settings (continued)

Register Name Field Name

TPS65941120-Q1 TPS65941421-Q1 LP876411B5-Q1

Value Description Value Description Value Description

MASK_BUCK1_2 BUCK1_ILIM_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK1_OV_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK1_UV_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK2_ILIM_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK2_OV_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK2_UV_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

MASK_BUCK3_4 BUCK3_ILIM_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK3_OV_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK3_UV_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK4_OV_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK4_UV_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

BUCK4_ILIM_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated 0x0 Interrupt generated

MASK_BUCK5 BUCK5_ILIM_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated

BUCK5_OV_MA

SK

0x0 Interrupt generated 0x0 Interrupt generated

BUCK5_UV_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated

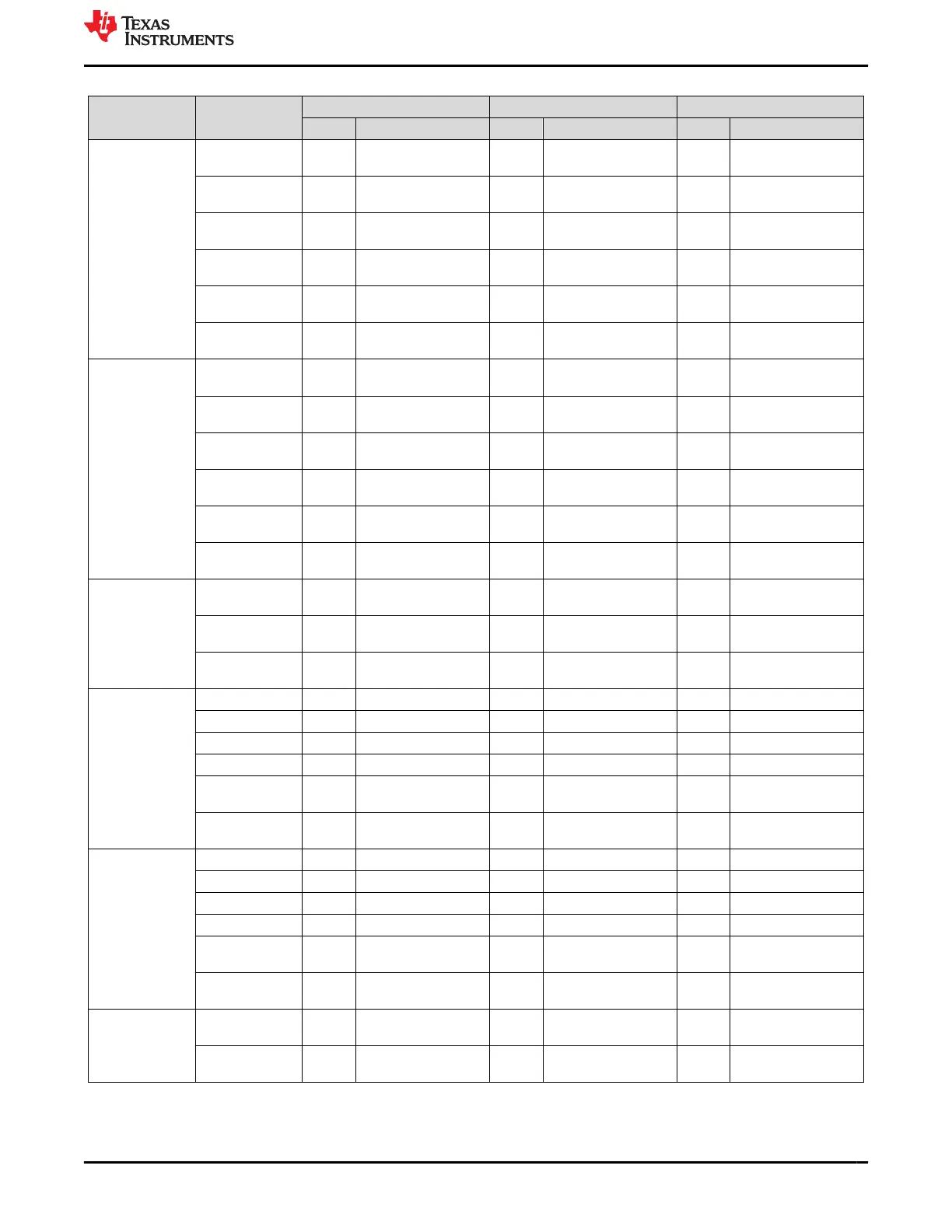

MASK_LDO1_2 LDO1_OV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO1_UV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO2_OV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO2_UV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO1_ILIM_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated

LDO2_ILIM_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated

MASK_LDO3_4 LDO3_OV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO3_UV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO4_OV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO4_UV_MASK 0x0 Interrupt generated 0x0 Interrupt generated

LDO3_ILIM_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated

LDO4_ILIM_MAS

K

0x0 Interrupt generated 0x0 Interrupt generated

MASK_VMON VCCA_OV_MAS

K

0x1 Interrupt not

generated.

(1)

0x1 Interrupt not

generated.

0x1 Interrupt not

generated.

VCCA_UV_MAS

K

0x1 Interrupt not

generated.

(1)

0x1 Interrupt not

generated.

0x1 Interrupt not

generated.

www.ti.com Static NVM Settings

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

25

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...