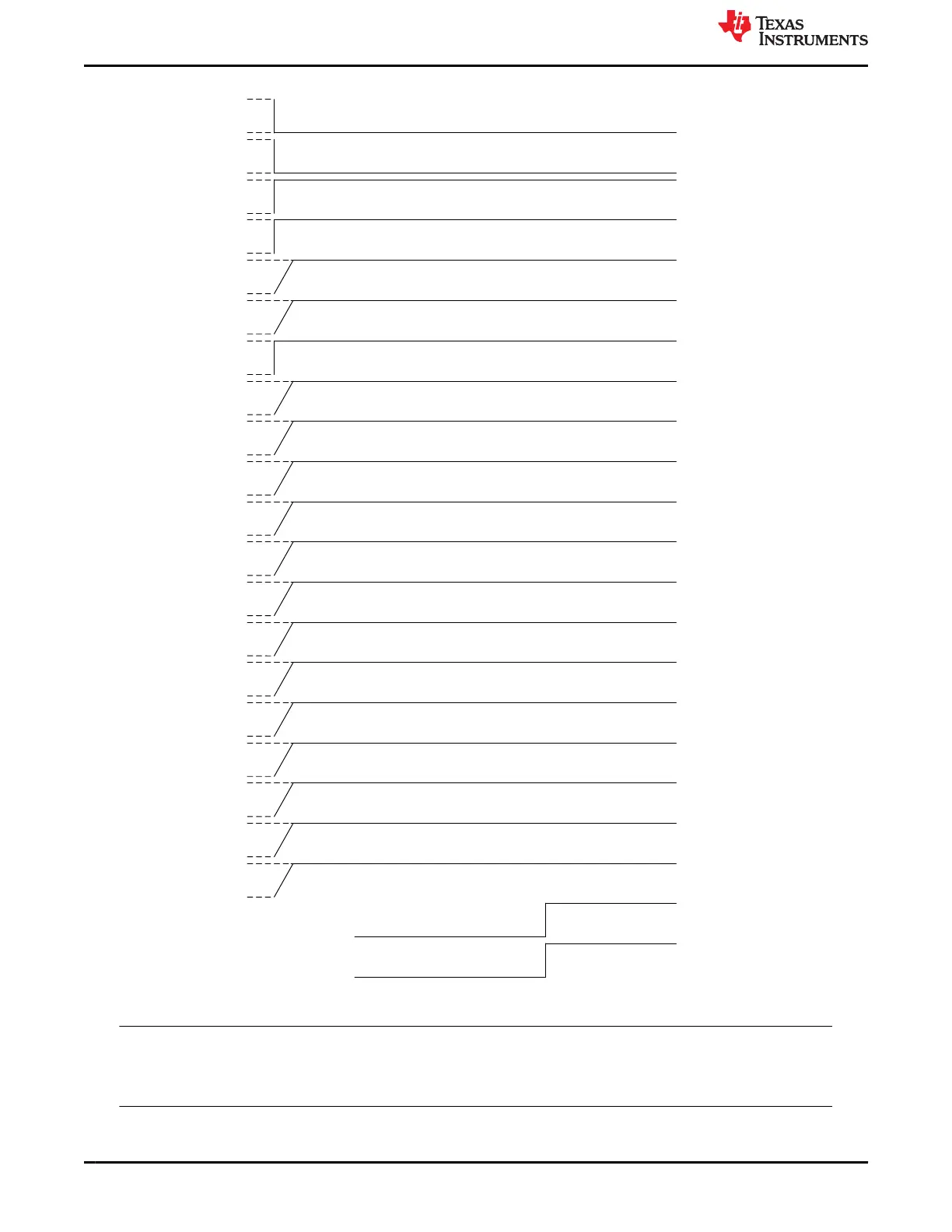

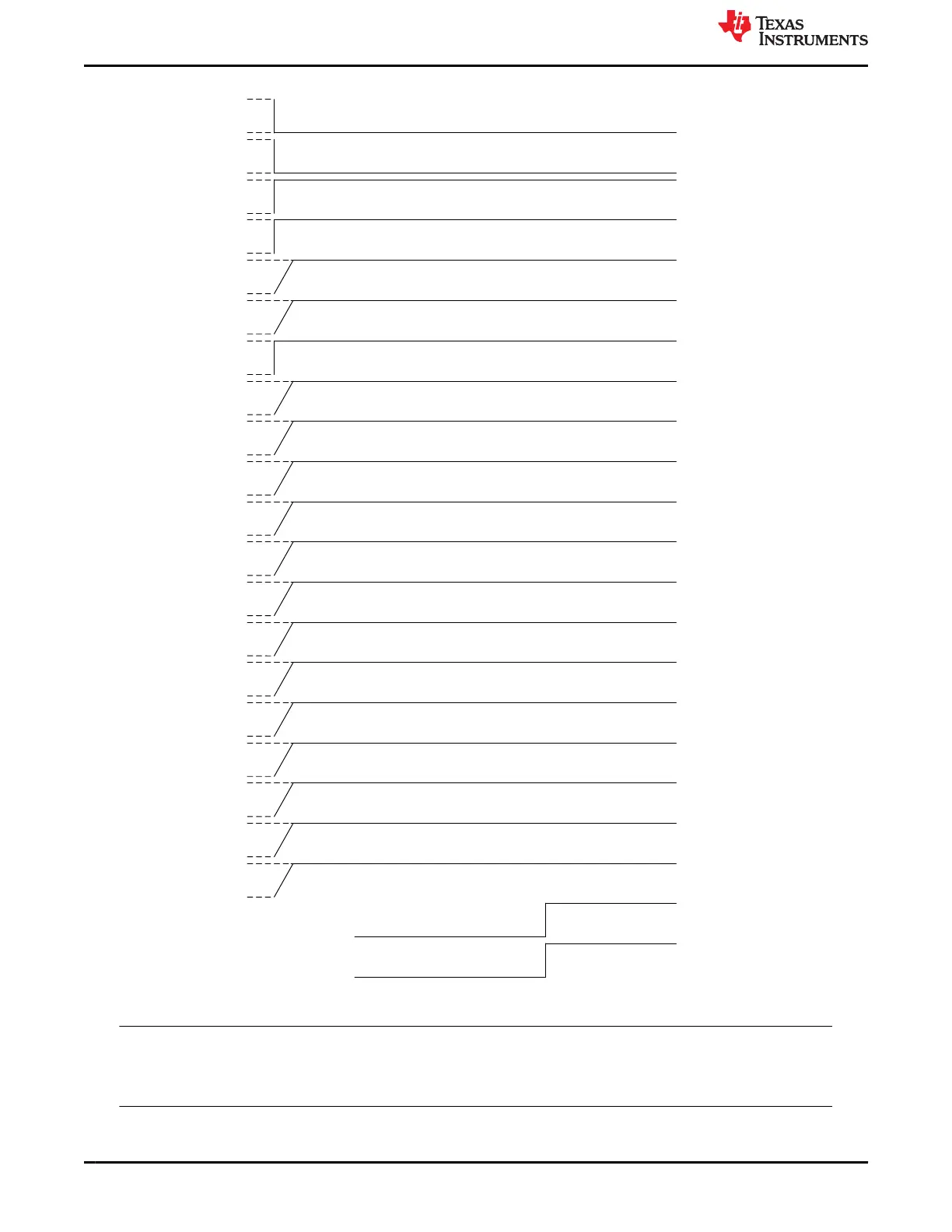

Resource PMIC Delay Diagram Total Delay Rail Name

GPIO9

TPS65941120-Q1

(Leo A)

0 us EN_MCU3V3_VIO

GPIO11

TPS65941421-Q1

(Leo B)

0 us EN_3V3_IO

LDO2

TPS65941120-Q1

(Leo A)

0 us

VDD_MCU_

GPIORET_3V3

LDO2

TPS65941421-Q1

(Leo B)

0 us VDD_GPIORET_3V3

GPIO3

TPS65941421-Q1

(Leo B)

0 us EN_DDR_VDD1

LDO4

TPS65941120-Q1

(Leo A)

0 us VDA_MCU_1V8

LDO3

TPS65941120-Q1

(Leo A)

0 us VDD_MCUIO_1V8

BUCK3

TPS65941421-Q1

(Leo B)

0 us VDD_PHY_1V8

BUCK1

TPS65941421-Q1

(Leo B)

0 us VDD_IO_1V8

LDO4

TPS65941421-Q1

(Leo B)

0 us VDD_PLL_1V8

BUCK5

TPS65941120-Q1

(Leo A)

0 us VDD_MCU_0V85

LDO1

TPS65941120-Q1

(Leo A)

0 us VDD_MCU_WK_0V8

BUCK1234

TPS65941120-Q1

(Leo A)

0 us VDD_CPU_AVS

BUCK1234

LP876411B5-Q1

(Hera C)

0 us VDD_CORE_0V8

LDO1

TPS65941421-Q1

(Leo B)

0 us VDD_WK_0V8

LDO3

TPS65941421-Q1

(Leo B)

0 us VDA_DLL_0V8

BUCK5

TPS65941421-Q1

(Leo B)

0 us VDD_RAM_0V85

BUCK4

TPS65941421-Q1

(Leo B)

0 us VDD_DDR_1V1

nRSTOUT

TPS65941120-Q1

(Leo A)

2000 us H_MCU_PORz

GPIO11

TPS65941120-Q1

(Leo A)

2000 us H_SOC_PORz

nRSTOUT

TPS65941120-Q1

(Leo A)

0 us H_MCU_PORz

GPIO11

TPS65941120-Q1

(Leo A)

0 us H_SOC_PORz

Figure 6-4. ACTIVE_TO_WARM Power Sequence

Note

The regulator transitions do not represent enabling of the regulators but the time at which the voltages

are restored to their default values. Since this sequence originates from the ACTIVE state all of the

regulators are on.

Pre-Configurable Finite State Machine (PFSM) Settings www.ti.com

40 TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...