6.3.4 ESM_SOC_ERROR

In the event of an ESM_SOC error, the nRSTOUT_SOC signal is driven low and then driven high again after 200

µs. There is no change to the power rails. The sequence is shown in Figure 6-5.

Resource

nRSTOUT_SOC TPS65941120-Q1

PMIC Delay Diagram Total Delay Rail Name

0 us H_SOC_PORz_1V8

nRSTOUT_SOC TPS65941120-Q1 200 us H_SOC_PORz_1V8

Figure 6-5. ESM_SOC_ERROR Sequence

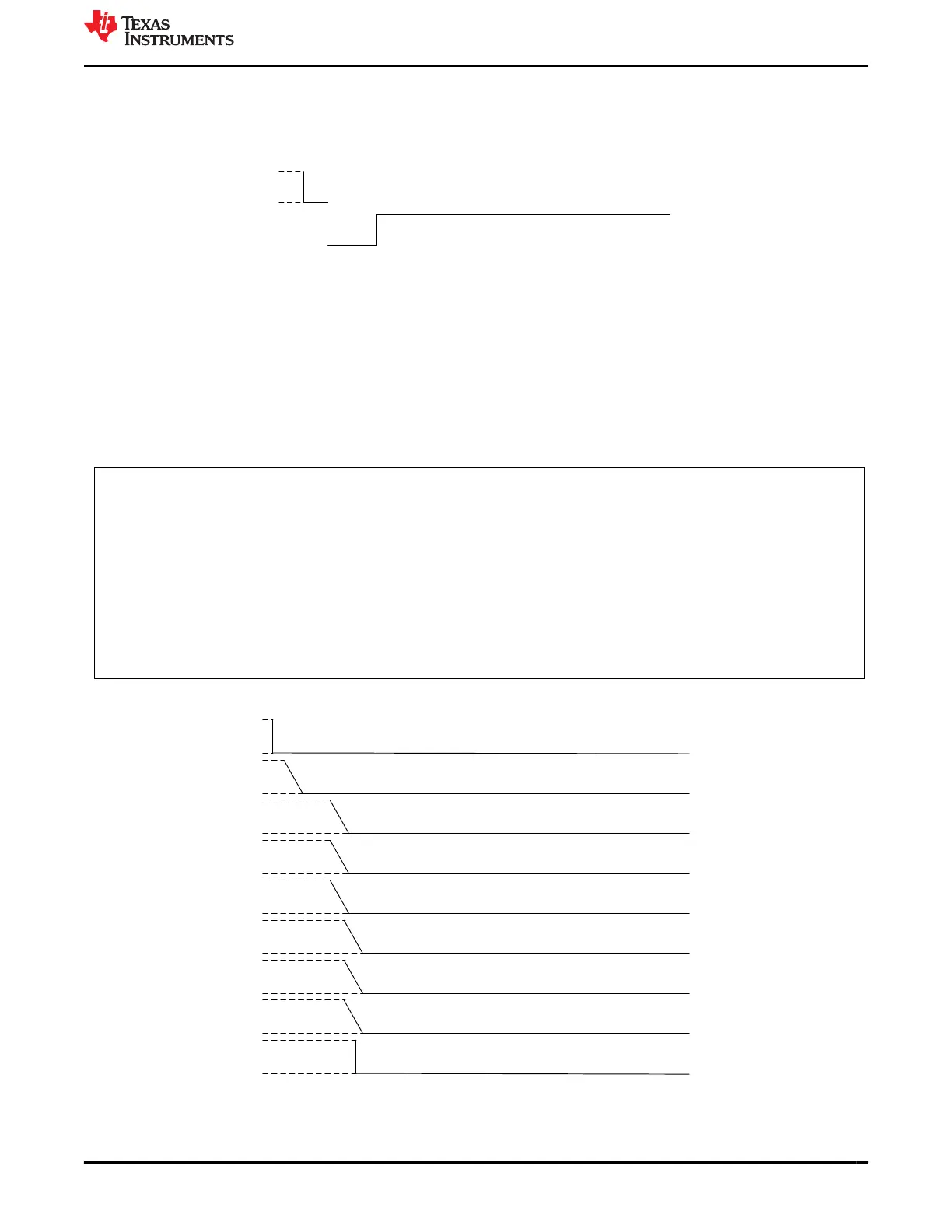

6.3.5 PWR_SOC_ERROR

In the event of an error on any of the power rails which are part of the SOC power rail group, the

PWR_SOC_ERROR sequence is performed. The nRSTOUT_SOC pin is pulled low and the SOC power rails

execute a normal processor power down sequence except the MCU power group remains energized as shown

in Figure 6-6. The state of the I2C_7 trigger in both TPS6594-Q1 devices determines whether the DDR supplies

and control signal remain energized (I2C_7=1) or disabled (I2C_7=0). The I2C_6 trigger in both TPS6594-Q1

devices determines whether the SOC GPIO retention supplies remain energized.

In the start of the sequence the following instructions are executed:

// TPS65941120

// Set AMUXOUT_EN and CLKMON_EN, clear LPM_EN and nRSTOUT_SOC

REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x18 MASK=0xE1

// Clear SPMI_LPM_EN

REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x00 MASK=0xEF

//TPS65941421

// Set AMUXOUT_EN and CLKMON_EN, clear LPM_EN

REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x18 MASK=0xE3

// Clear SPMI_LPM_EN

REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x00 MASK=0xEF

//LP876411B5

// Set CLKMON_EN, clear LPM_EN

REG_WRITE_MASK_IMM ADDR=0x81 DATA=0x08 MASK=0xF3

// Clear SPMI_LPM_EN

REG_WRITE_MASK_IMM ADDR=0x82 DATA=0x00 MASK=0xEF

Resource PMIC Delay Diagram Total Delay Rail Name

GPIO11

(nRSTOUT_SOC)

TPS65941120-Q1

(Leo A)

0 us H_SOC_PORz

BUCK5

TPS65941421-Q1

(Leo B)

500 us VDD_RAM_0V85

LDO3

TPS65941421-Q1

(Leo B)

2500 us VDA_DLL_0V8

BUCK1234

LP876411B5-Q1

(Hera C)

2500 us VDD_CORE_0V8

BUCK1234

TPS65941120-Q1

(Leo A)

2500 us VDD_CPU_AVS

LDO4

TPS65941421-Q1

(Leo B)

3000 us VDD_PLL_1V8

BUCK1

TPS65941421-Q1

(Leo B)

3000 us VDD_IO_1V8

BUCK3

TPS65941421-Q1

(Leo B)

3000 us VDD_PHY_1V8

GPIO11

TPS65941421-Q1

(Leo B)

3500 us EN_3V3_VIO

Figure 6-6. PWR_SOC_ERROR with I2C Triggers High in both PMICs

www.ti.com Pre-Configurable Finite State Machine (PFSM) Settings

SLVUCJ9 – FEBRUARY 2023

Submit Document Feedback

TPS65941120-Q1, TPS65941421-Q1 and LP876411B5-Q1 PMIC User Guide

for J721S2, PDN-0A

41

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...