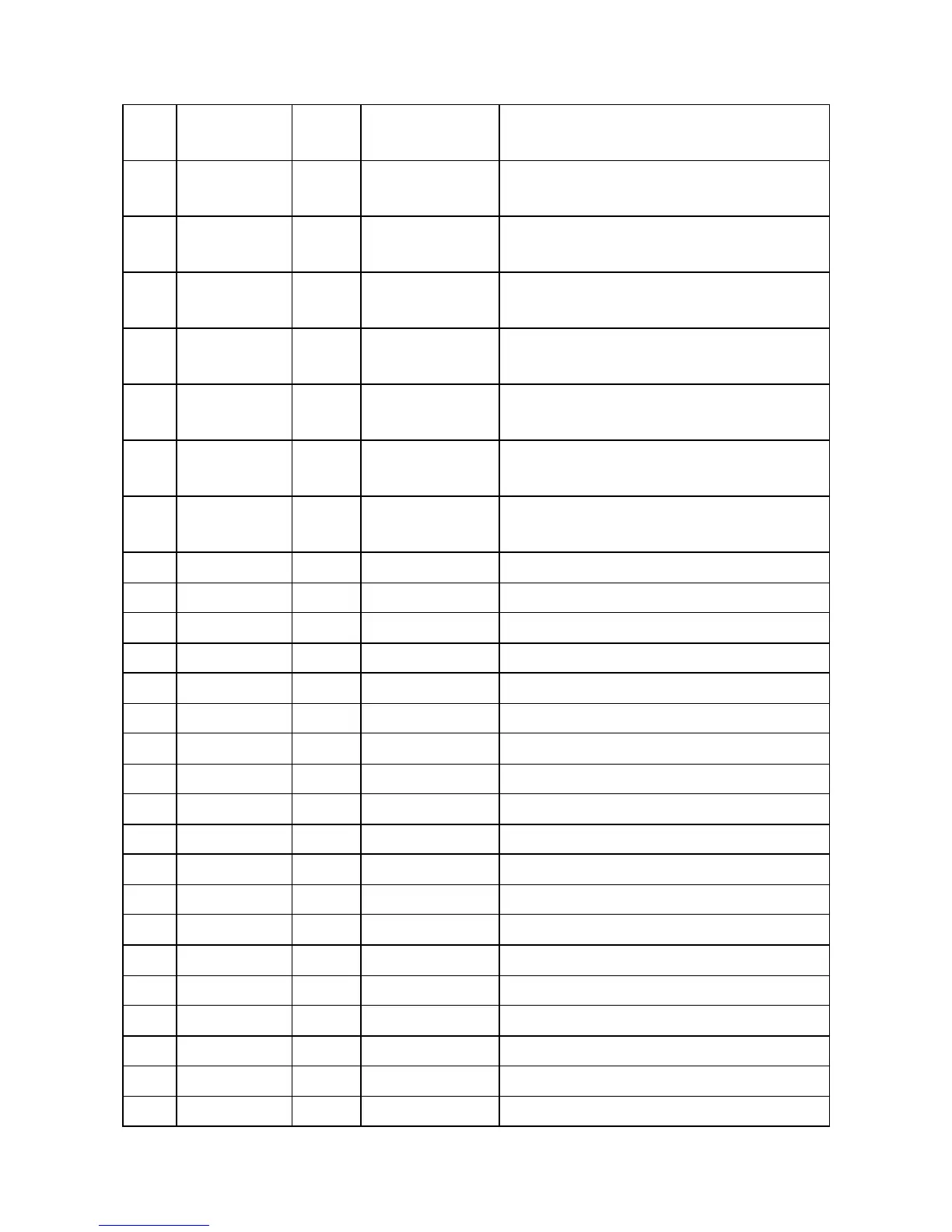

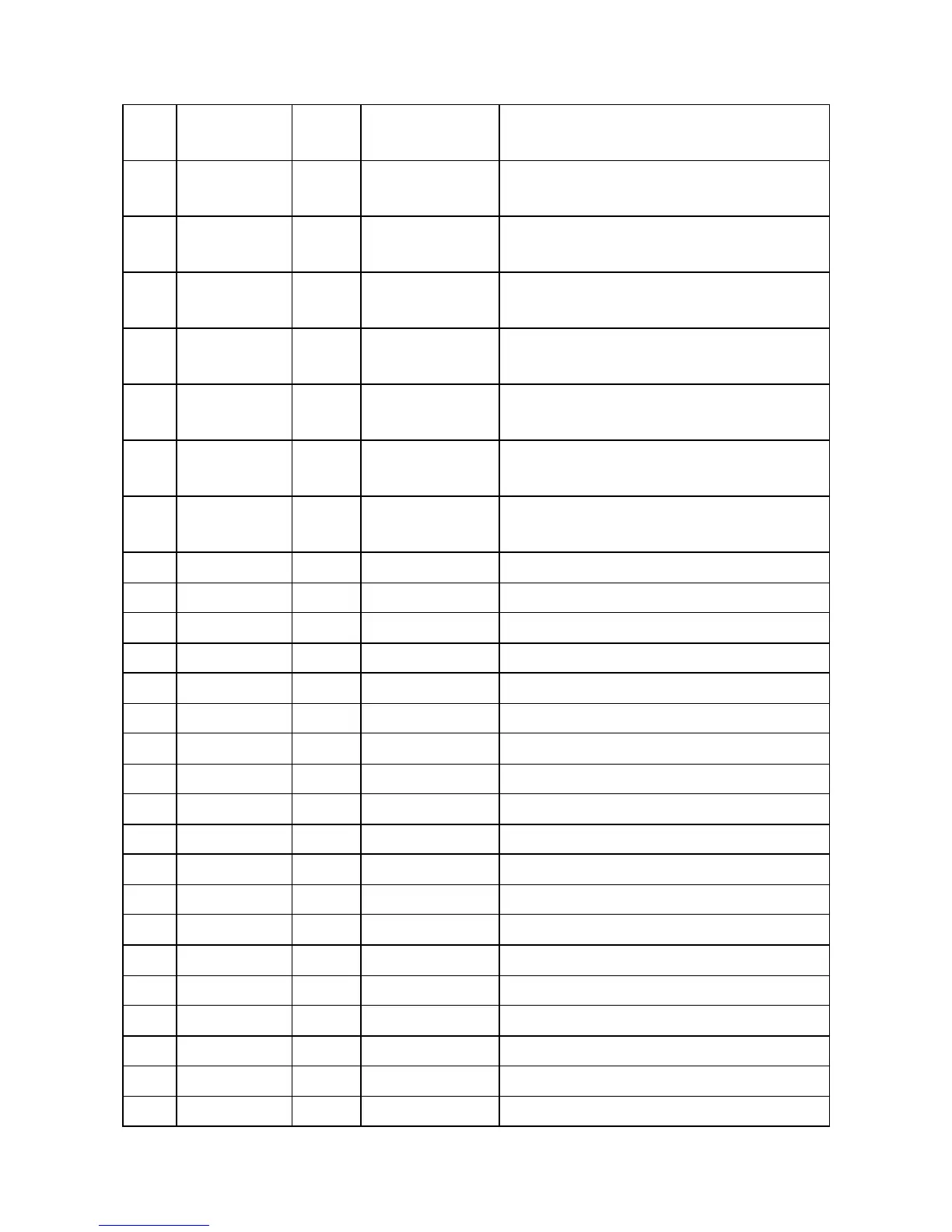

165 Y_0

IO_9(RD2

4)

InOut Non-pull

1) Digital Video output Y bit 0

2) GPIO

164 Y_1

IO_10(RD

25)

InOut Non-pull

1) Digital Video output Y bit 1

2) GPIO

163 Y_2

IO_11(RD

26)

InOut Non-pull

1) Digital Video output Y bit 2

2) GPIO

162 Y_3

IO_12(RD

27)

InOut Non-pull

1) Digital Video output Y bit 3

2) GPIO

161 Y_4

IO_13(RD

28)

InOut Non-pull

1) Digital Video output Y bit 4

2) GPIO

159 Y_5

IO_14(RD

29)

InOut Non-pull

1) Digital Video output Y bit 5

2) GPIO

158 Y_6

IO_15(RD

30)

InOut Non-pull

1) Digital Video output Y bit 6

2) GPIO

157 Y_7

IO_16(RD

31)

InOut Non-pull

1) Digital Video output Y bit 7

2) GPIO

155 RA 4 InOut DRAM address 4

154 RA 5 InOut DRAM address 5

153 RA 6 InOut DRAM address 6

152 RA 7 InOut DRAM address 7

151 RA 8 InOut DRAM address 8

150 RA 9 InOut DRAM address 9

149 RA 11 InOut DRAM address bit 11

147 CKE InOut Pull-Down DRAM clock enable

146 RCLK InOut Dram clock

144 RA 3 InOut DRAM address 3

143 RA 2 InOut DRAM address 2

141 RA 1 InOut DRAM address 1

140 RA 0 InOut DRAM address 0

139 RA 10 InOut DRAM address 10

138 BA1 InOut DRAM bank address 1

137 BA0 InOut DRAM bank address 0

136 RCS# output DRAM chip select, active low

135 RAS# output DRAM row address strobe, active low

134 CAS# output DRAM column address strobe, active low

- 67 -

Loading...

Loading...