The bit-planes for a full-screen-sized, interlaced display are 400 NTSC (512 PAL), rather

than 200 NTSC (256 PAL), lines long. Assuming that the playfield in memory is the normal

320 pixels wide, data for the interlaced picture begins at the following locations (these are

all byte addresses):

Line 1 START

Line 2 START+40

Line 3 START+80

Line 4 START+120

and so on. Therefore, you use a modulo of 40 to skip the lines in the other field. For odd

fields, the bit-plane pointers begin at START. For even fields, the bit-plane pointers begin

at START+40

You can use the Copper to handle resetting of the bit-plane pointers for interlaced

displays.

DISPLAYING AND REDISPLAYING THE PLAYFIELD

You start playfield display by making certain that The bit-plane pointers are set and bit-

plane DMA is turned on. You turn on bit-plane DMA by writing a 1 to bit BPLEN in the

DMACON (for DMA control) register. See Chapter 7, "System Control Hardware," for

instructions on setting this register.

Each time The playfield is redisplayed, you have to reset the bit-plane pointers. Resetting

is necessary because the pointers have been incremented to point to each successive

word in memory and must be repointed to the first word for the next display. You write

Copper instructions to handle the redisplay or perform this operation as part of a vertical

blanking task.

ENABLING THE COLOR DISPLAY

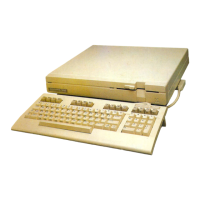

The stock A1000 has a color composite output and requires bit 9 set in BPLCON0 to create

a color composite display signal. Without the addition of specialized hardware, the A500

and A2000 cannot generate color composite output.

NOTE

The color burst enable does not affect the RGB video signal. RGB video is correctly

generated regardless of the output of the composite video signal.

- 56 Playfield Hardware -

Loading...

Loading...