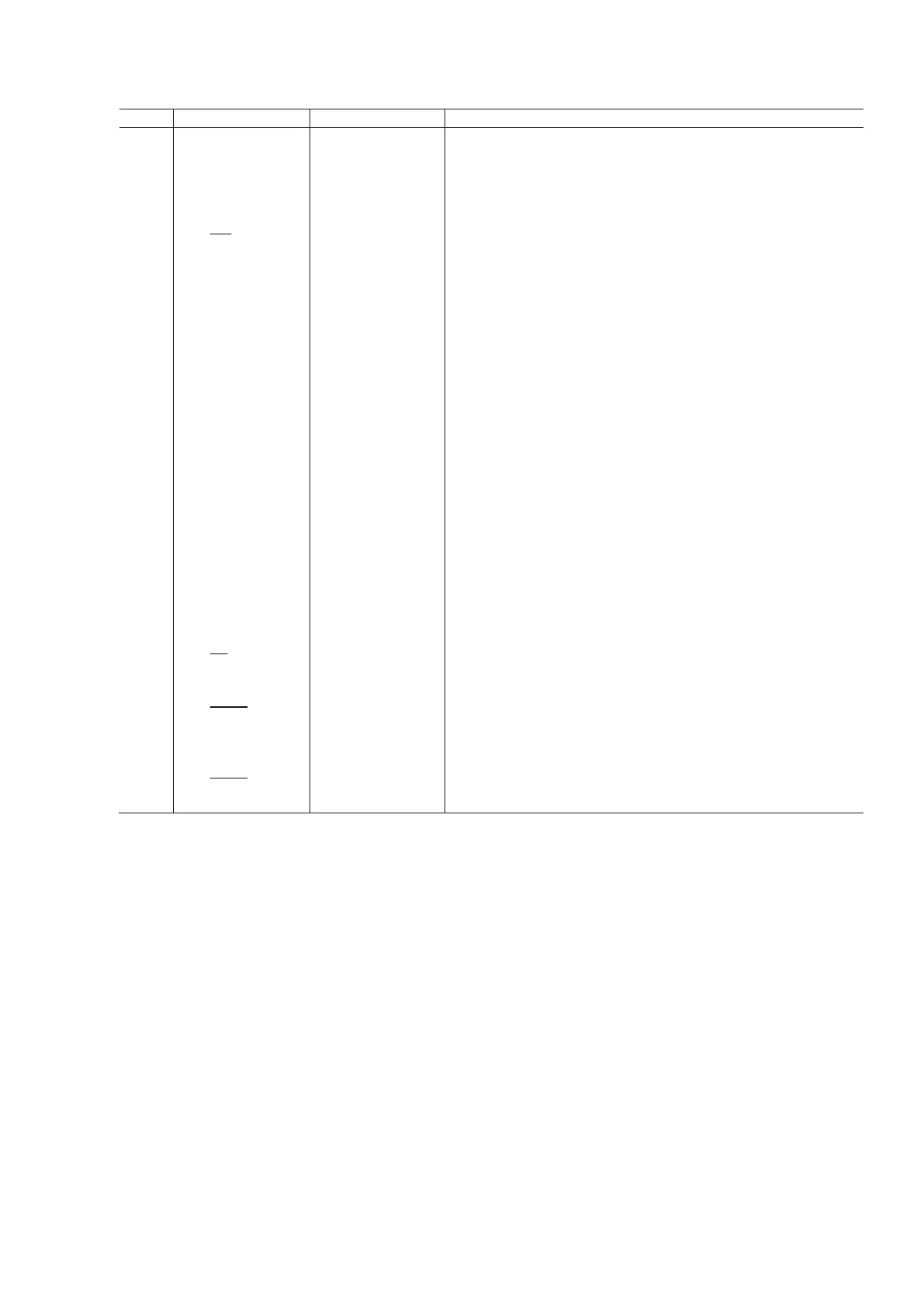

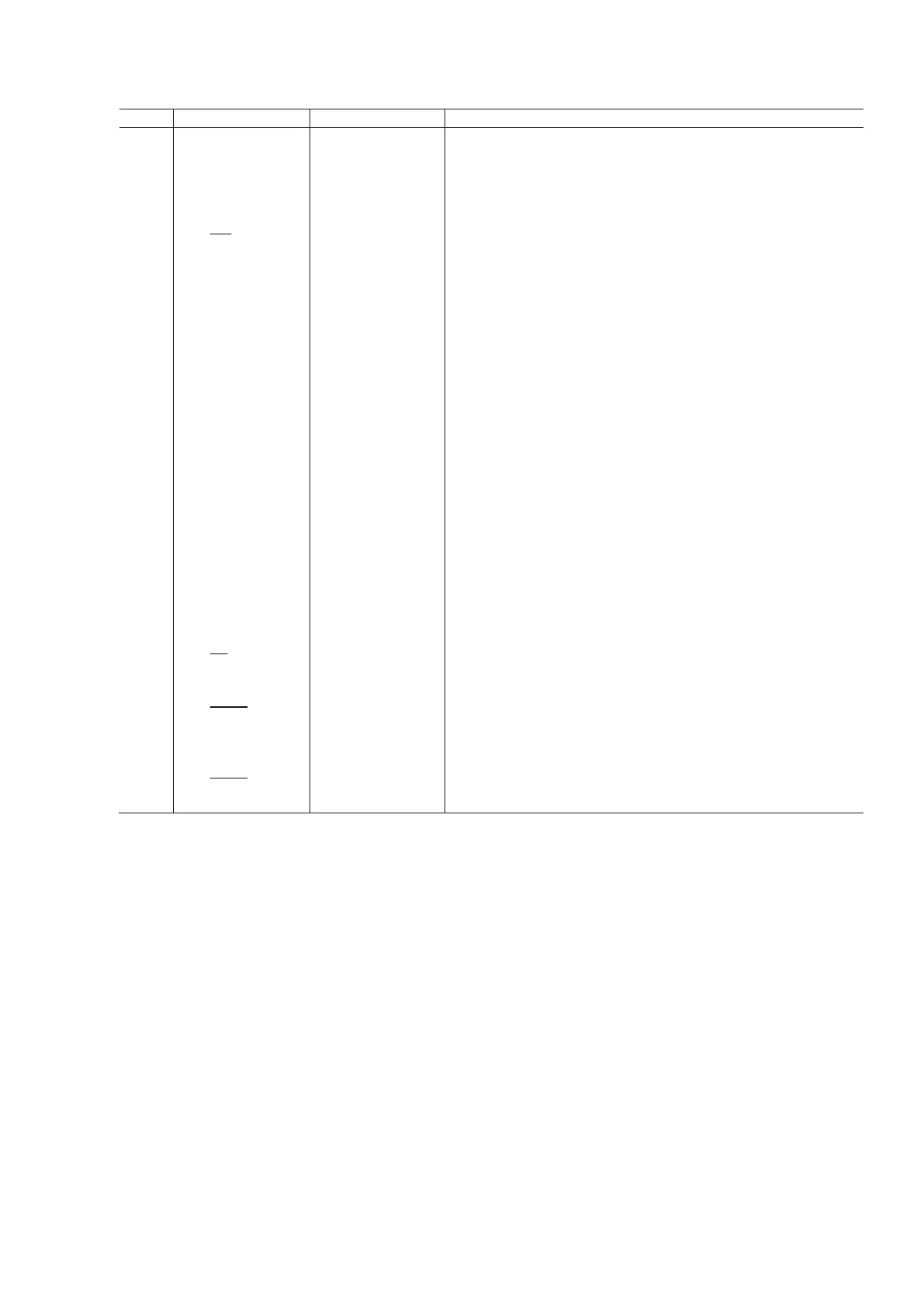

235

Pin No. Mnemonic Type Description

AB8 DDR_DQ[29] DDR interface Data Line. Interface to external RAM data lines.

AB9 DDR_A[12] DDR interface Address Line. Interface to external RAM address lines.

AB10 DDR_A[6] DDR interface Address Line. Interface to external RAM address lines.

AB11 DDR_A[3] DDR interface Address Line. Interface to external RAM address lines.

AB12 DDR_A[0] DDR interface Address Line. Interface to external RAM address lines.

AB13 DDR_BA[0] DDR interface Bank Address Line. Indicates which data bank to write/read from.

AB14

DDR_RAS

DDR interface Row Address Strobe for DDR Memory.

AB15 DDR_CKE DDR interface Clock Enable for External DDR Memory.

AB16 DDR_DQ[12] DDR interface Data Line. Interface to external RAM data lines.

AB17 DDR_DQS[1] DDR interface Data Strobe for DDR Data Bytes[15:8].

AB18 DDR_DQ[8] DDR interface Data Line. Interface to external RAM data lines.

AB19 DDR_DQ[13] DDR interface Data Line. Interface to external RAM data lines.

AB20 DDR_DQ[0] DDR interface Data Line. Interface to external RAM data lines.

AB21 DDR_DQ[5] DDR interface Data Line. Interface to external RAM data lines.

AB22 DDR_DQS[0] DDR interface Data Strobe for DDR Data Bytes[7:0].

AB23 DDR_DQ[4] DDR interface Data Line. Interface to external RAM data lines.

AC1 DDR_DQ[16] DDR interface Data Line. Interface to external RAM data lines.

AC2 DDR_DQ[20] DDR interface Data Line. Interface to external RAM data lines.

AC3 DDR_DQ[22] DDR interface Data Line. Interface to external RAM data lines.

AC4 DDR_DQ[25] DDR interface Data Line. Interface to external RAM data lines.

AC5 DDR_DQ[28] DDR interface Data Line. Interface to external RAM data lines.

AC6 DDR_DQ[27] DDR interface Data Line. Interface to external RAM data lines.

AC7 DDR_DQ[24] DDR interface Data Line. Interface to external RAM data lines.

AC8 DDR_A[9] DDR interface Address Line. Interface to external RAM address lines.

AC9 DDR_A[5] DDR interface Address Line. Interface to external RAM address lines.

AC10 DDR_A[7] DDR interface Address Line. Interface to external RAM address lines.

AC11 DDR_A[1] DDR interface Address Line. Interface to external RAM address lines.

AC12 DDR_A[10] DDR interface Address Line. Interface to external RAM address lines.

AC13 DDR_BA[1] DDR interface Bank Address Line. Indicates which data bank to write/read from.

AC14 DDR_BA[2] DDR interface Bank Address Line. Indicates which data bank to write/read from.

AC15

DDR_WE

DDR interface Write Enable Signal for DDR RAM.

AC16 DDR_VREF DDR interface

1

Reference Voltage for DDR RAM.

AC17 DDR_DQ[10] DDR interface Data Line. Interface to external RAM data lines.

AC18

DDR_DQS[1]

DDR interface Data Strobe for DDR Data Byte[15:8].

AC19 DDR_DQ[15] DDR interface Data Line. Interface to external RAM data lines.

AC20 DDR_DQ[7] DDR interface Data Line. Interface to external RAM data lines.

AC21 DDR_DQ[2] DDR interface Data Line. Interface to external RAM data lines.

AC22

DDR_DQS[0]

DDR interface Data Strobe for DDR Data Byte[7:0].

AC23 DDR_DQ[1] DDR interface Data Line. Interface to external RAM data lines.

1

Sensitive node. Careful layout is important. The associated circuitry should be kept as close as possible to the ADV8003.

Loading...

Loading...