User Guide • SC3-LARGO • CompactPCI

®

Serial CPU Board • Intel

®

Core

TM

5xxx Processor

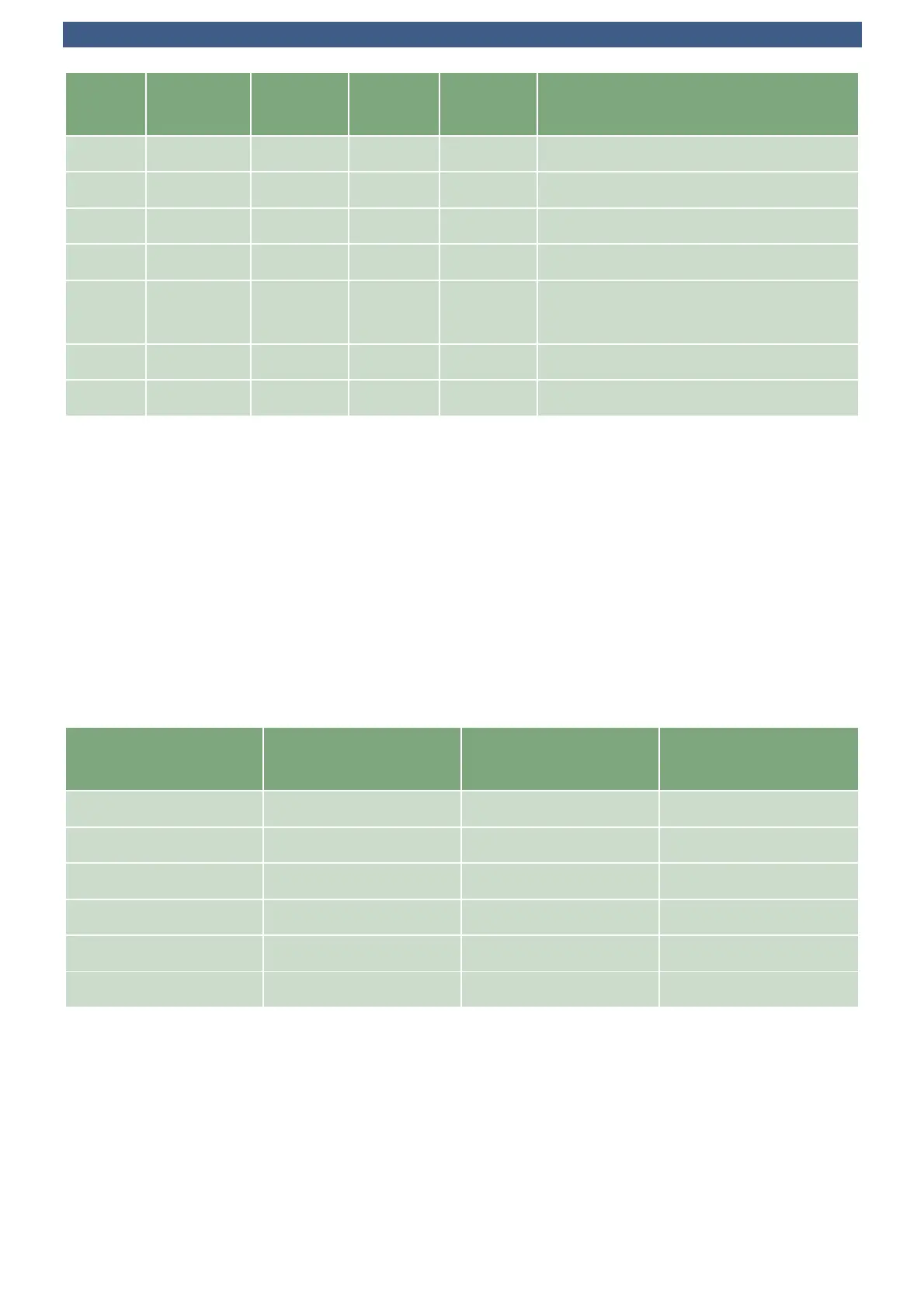

Bus # Device # Function

#

Vendor

ID

Device ID Description

0 31 6 0x8086 0x8C24 Thermal Controller

1

3)

00 0 0x1B4B 0x9230 SATA Host Controller (88SE9230)

2

3)

00 0 0x8086 0x157B Ethernet Controller NC2 (i210IT)

3

3)

00 0 0x10B5 0x8618 PCIe Switch Root Port (PEX8618)

4

3)

01,02,04

...

0 0x10B5 0x8618 PCIe Switch Downstream Ports

(PEX8618)

5

3)

00 0 0x8086 0x157B Ethernet Controller NC3 (i210IT)

6

3)

00 0 0x8086 0x157B Ethernet Controller NC4 (i210IT)

1)

Depends on BIOS settings.

2)

Depending on BIOS settings different RAID modes may lead to other Device IDs.

3)

Bus number can vary depending on the PCI enumeration schema implemented in BIOS.

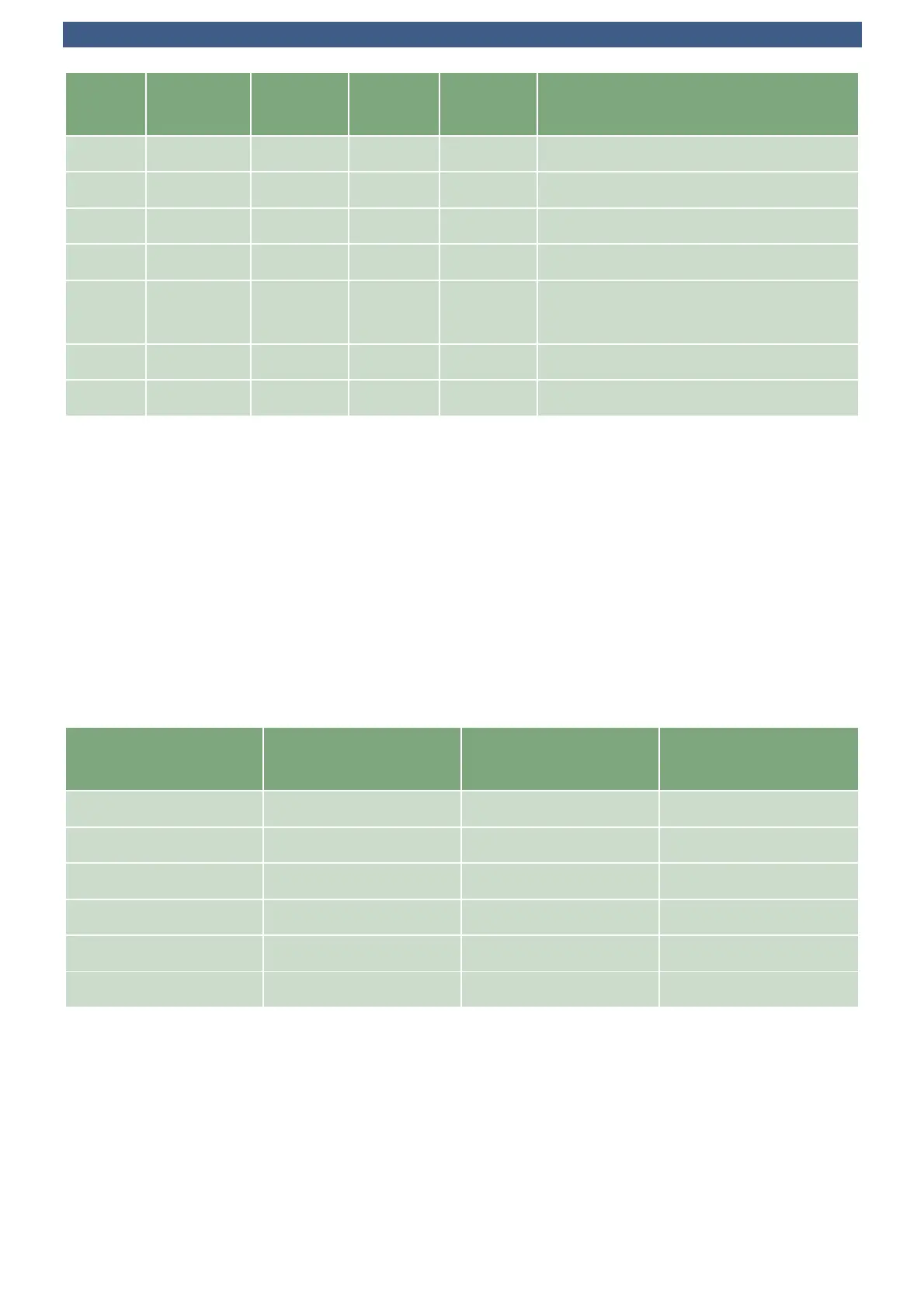

Physical Routing (Bus Numbering)

of the PEX 8618 PCIe Switch Ports/Lanes to the CompactPCI® Serial Backplane

PEX 8618

Port

PEX 8618

Lane

CPU (System Slot)

Connector

Targeted

Backplane Slot

2 4 P4 3_PE 4 of 9

10 5 P4 4_PE 5 of 9

12 6 P4 5_PE 6 of 9

14 7 P4 6_PE 7 of 9

13 14 P5 7_PE 8 of 9

15 15 P5 8_PE 9 of 9

Please note that the PEX 8618 ports are not assigned to backplane slots in an ascending order with

respect to the PCIe switch ports 13/14. The BIOS PCI bus enumeration algorithm as of current (2018-

02) follows exactly the PEX 8618 port number, not the lane number. Since this may cause some

irritation, we are currently considering a port swapping within future BIOS releases - check for updates

regularly.

© EKF -65- ekf.com

Loading...

Loading...