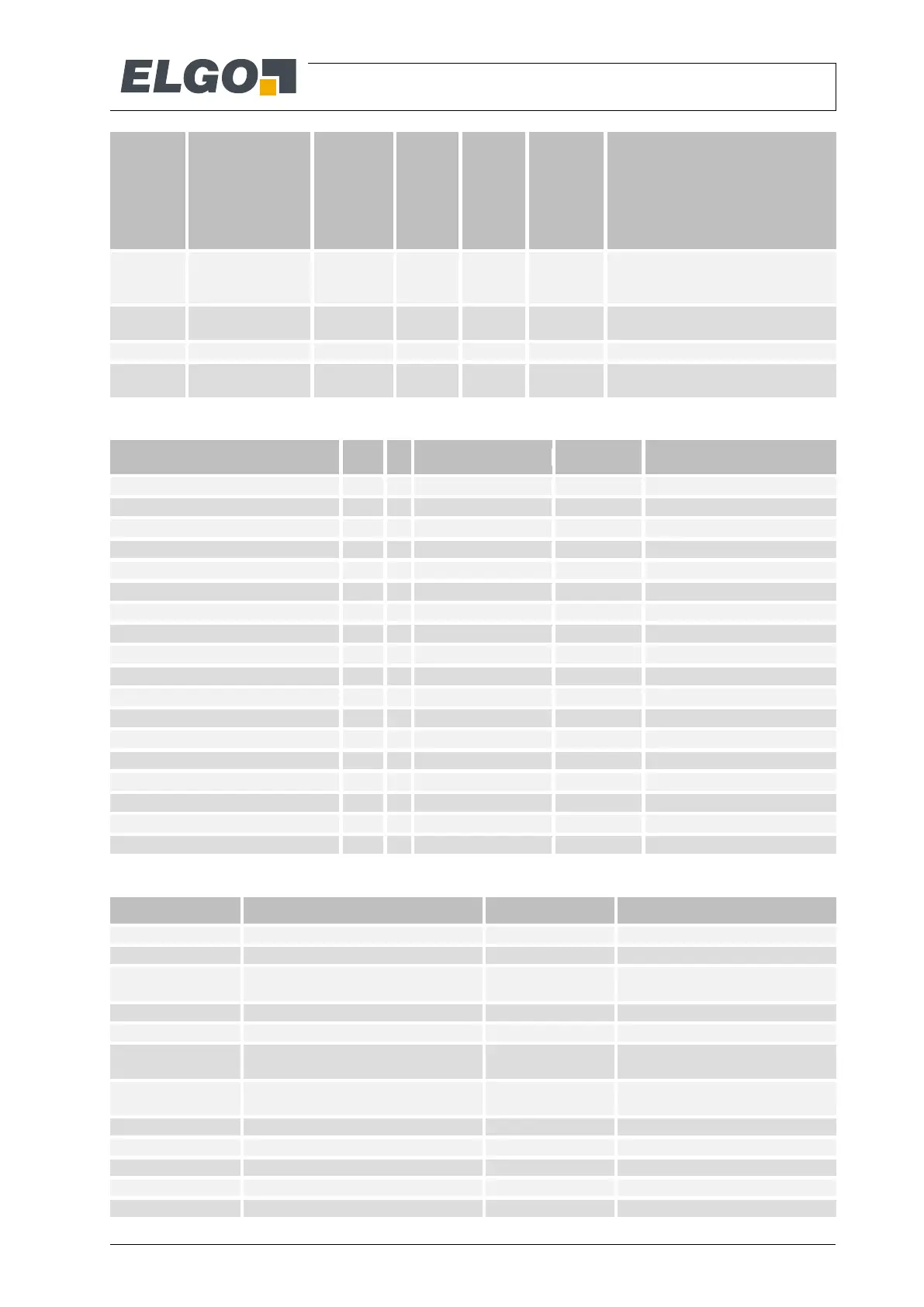

Required SIL

due to

EN81 (or

due to risk

analysis,

refer to

comments)

Achieved

SIL due

to PFHD

and SFF

Percentage

of required

SIL

ing system, the better values are valid

(eSGC would secure a failure of OC

in this case).

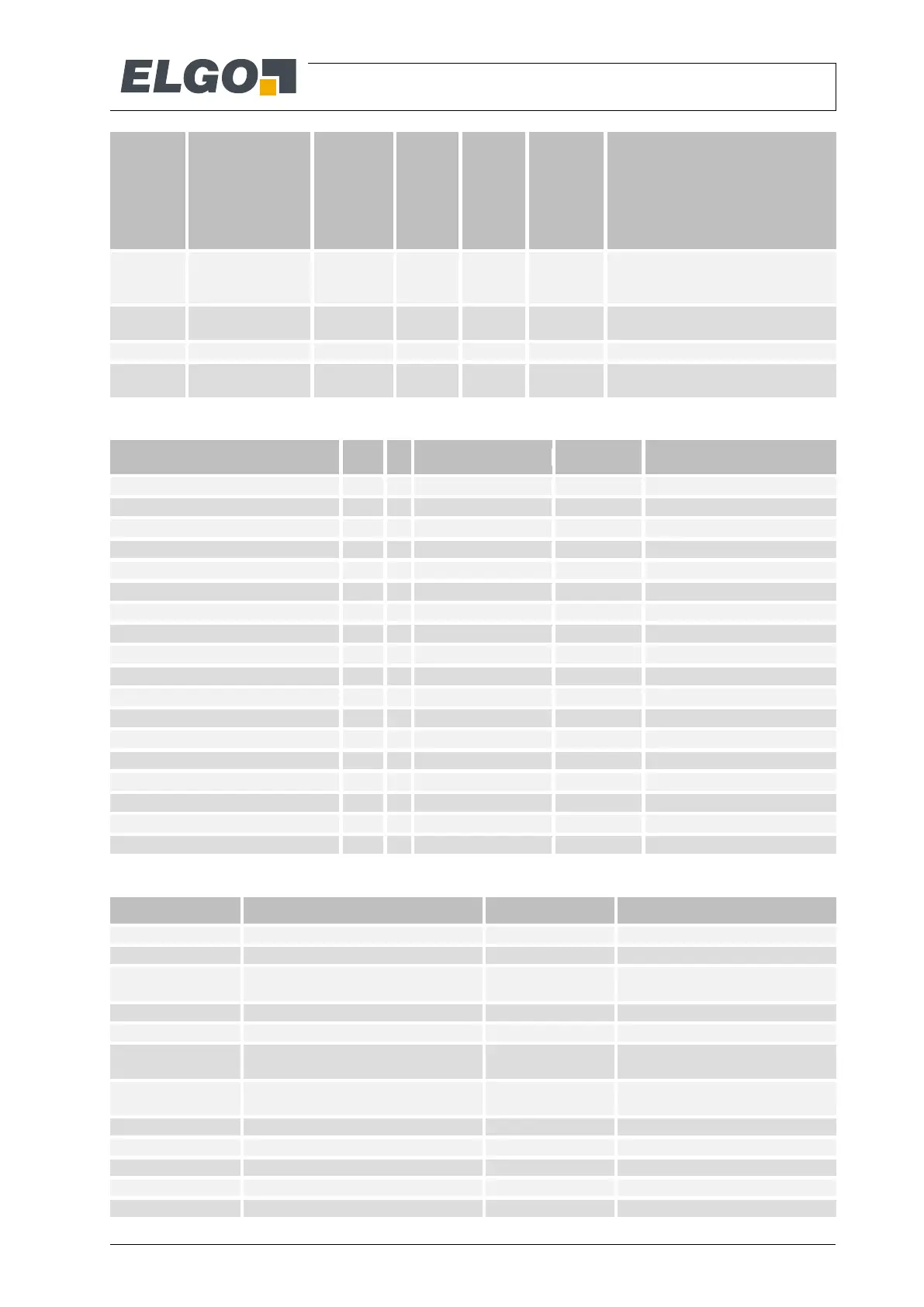

Table 27: Safe failure fraction, HFT and Type of the subsystems

Logic (µ-controller in the broad sense)

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Diagnostics for digital inputs

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

3.3 V and 2 V supply voltage

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Voltage supervision (diagnostics)

Required SFF for SIL3 achieved

External watchdog (diagnostics)

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Required SFF for SIL3 achieved

Table 28: Diagnostics Test Interval (DTI) of the subsystems

Comparison of the two channels

Plausibility of pattern of the analog

values

Plausibility of succession of positions

Dynamic check of analogue branch

Also 1 x complete at

startup before relays close

Also 1 x complete at

startup before relays close

Comparison with other channel

Loading...

Loading...