APPENDIX A <REFERENCE> EXTERNAL DEVICE INTERFACE TIMINGS

A-116 EPSON S1C33L03 PRODUCT PART

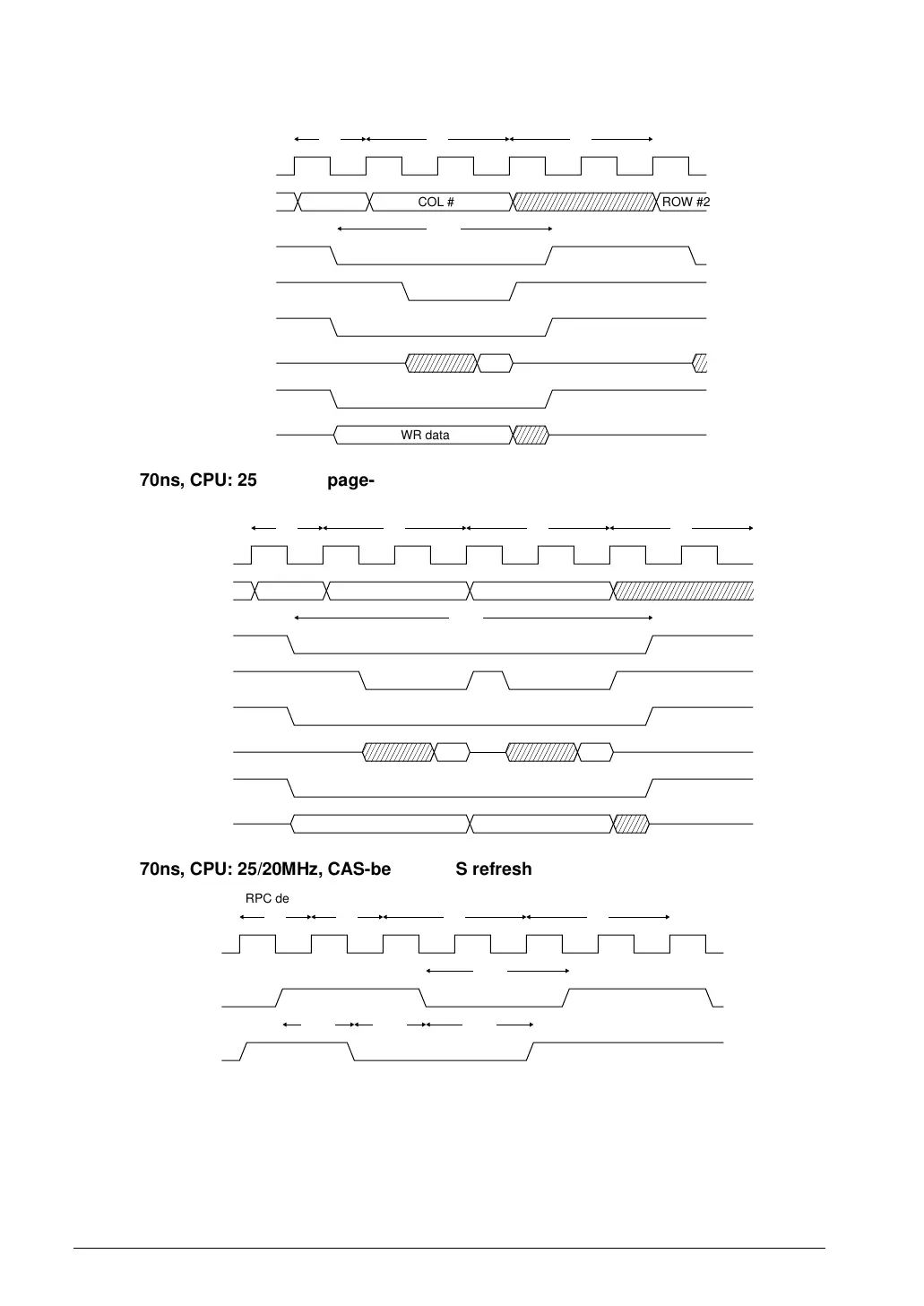

DRAM: 70ns, CPU: 25/20MHz, random read/write cycle

1

RAS cycle CAS cycle RAS precharge

2

t

RAS

2

BCLK

A[11:0]

#RAS

#CAS

#RD

D[15:0](RD)

#WE

D[15:0](WR)

ROW #1

RD data

ROW #2

WR data

COL #1

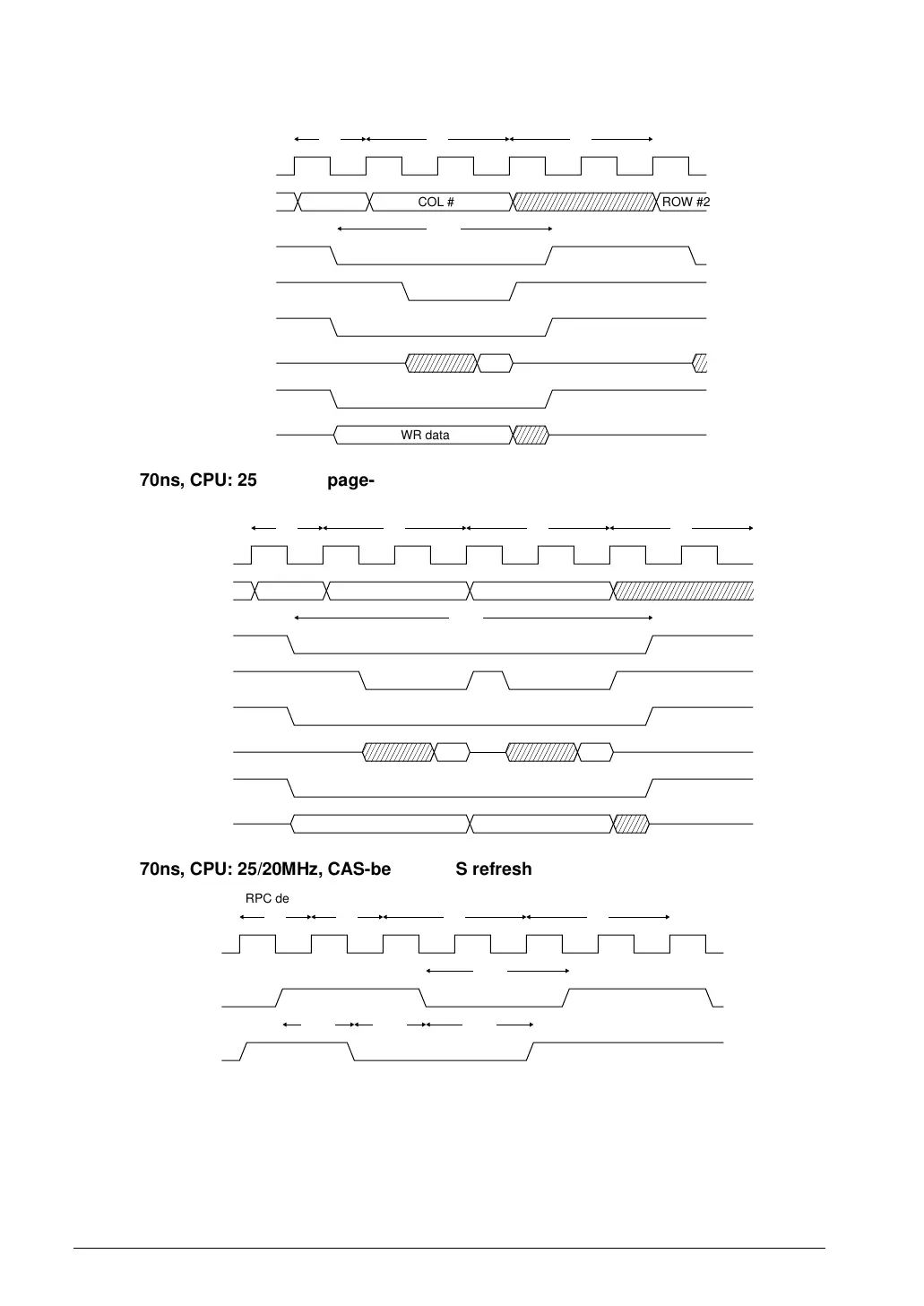

DRAM: 70ns, CPU: 25/20MHz, page-mode read/write cycle

1

RAS cycle CAS cycle RAS precharge

2

CAS cycle

2 2

tRAS

BCLK

A[11:0]

#RAS

#CAS

#RD

D[15:0](RD)

#WE

D[15:0](WR)

ROW #1

RD data

RD data

WR data

WR data

COL #1 COL #2

DRAM: 70ns, CPU: 25/20MHz, CAS-before-RAS refresh cycle

1 1

RPC delay Fixed Refresh RAS pulse width

2

RAS precharge

2

tRPC tCSR tCHR

tRAS

BCLK

#RAS

#CAS

Loading...

Loading...