II CORE BLOCK: INTRODUCTION

S1C33L03 FUNCTION PART EPSON B-II-1-1

A-1

B-II

Intro

II-1 INTRODUCTION

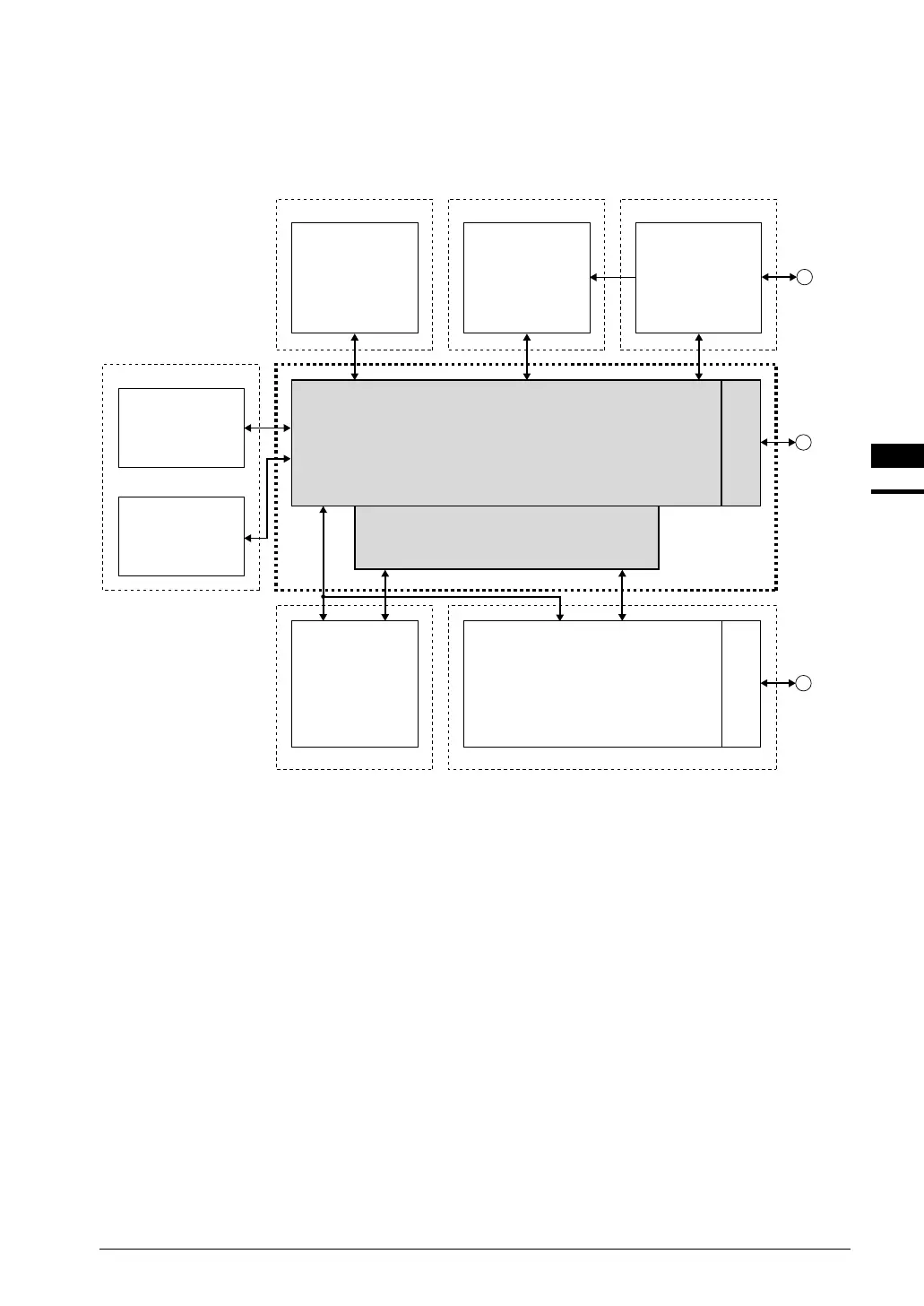

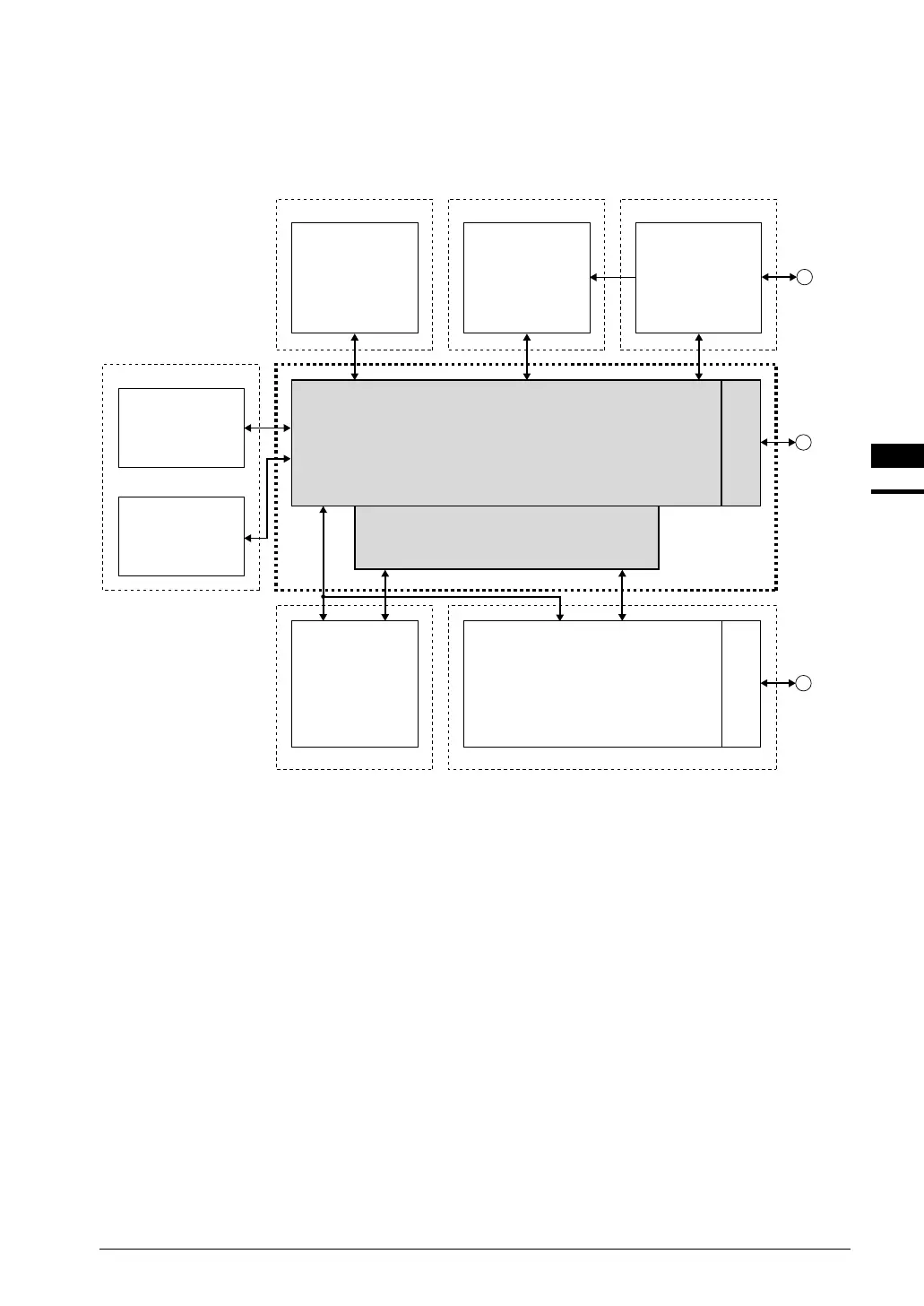

The core block consists of a functional block C33_CORE including CPU, BCU (Bus Control Unit), ITC

(Interrupt Controller), CLG (Clock Generator) and DBG (Debug Unit), an I/O pad block for external interface, and

an SBUS (Internal Silicon Integration Bus) for interfacing with on-chip Peripheral Macro Cells.

CORE_PAD

Pads

C33_SBUS

C33 Core Block

C33 LCD Controller Block

Pads

PERI_PAD

Pads

C33_PERI

(Prescaler, 8-bit timer, 16-bit timer,

Clock timer, Serial interface, Ports)

C33 Peripheral BlockC33 Analog Block

C33_CORE

(CPU, BCU, ITC, CLG, DBG)

C33_ADC

(A/D converter)

C33 Internal Memory Block

Internal RAM

(Area 0)

Internal ROM

(Area 10)

C33 DMA Block

C33_DMA

(IDMA, HSDMA)

C33_SDRAMC

(SDRAM interface)

C33_LCDC

(LCD panel interface)

C33 SDRAM Controller Block

Figure 1.1 Core Block

Note: Internal ROM is not provided in the S1C33L03.

Loading...

Loading...