VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

S1C33L03 FUNCTION PART EPSON B-VI-2-21

A-1

B-VI

SDRAM

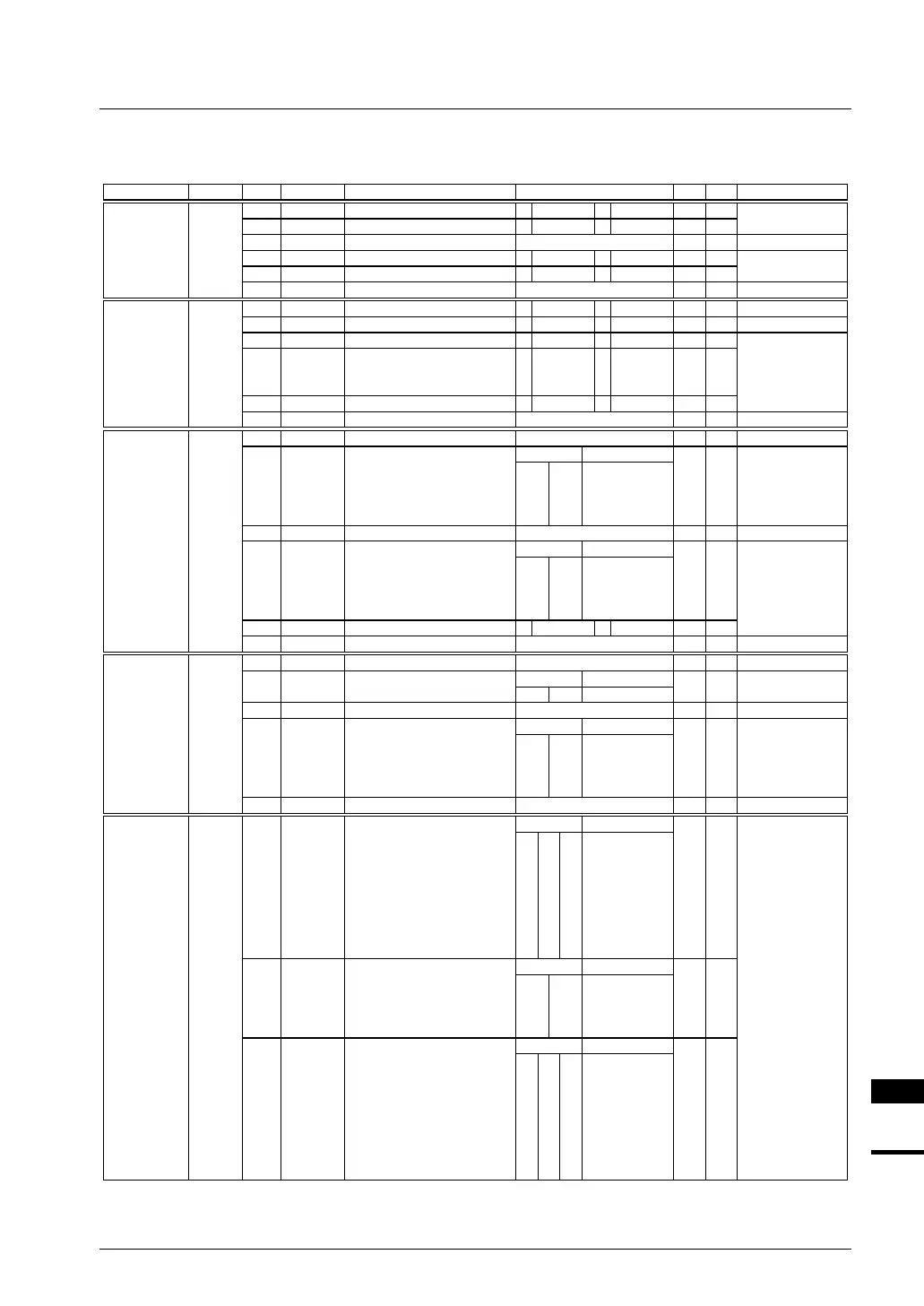

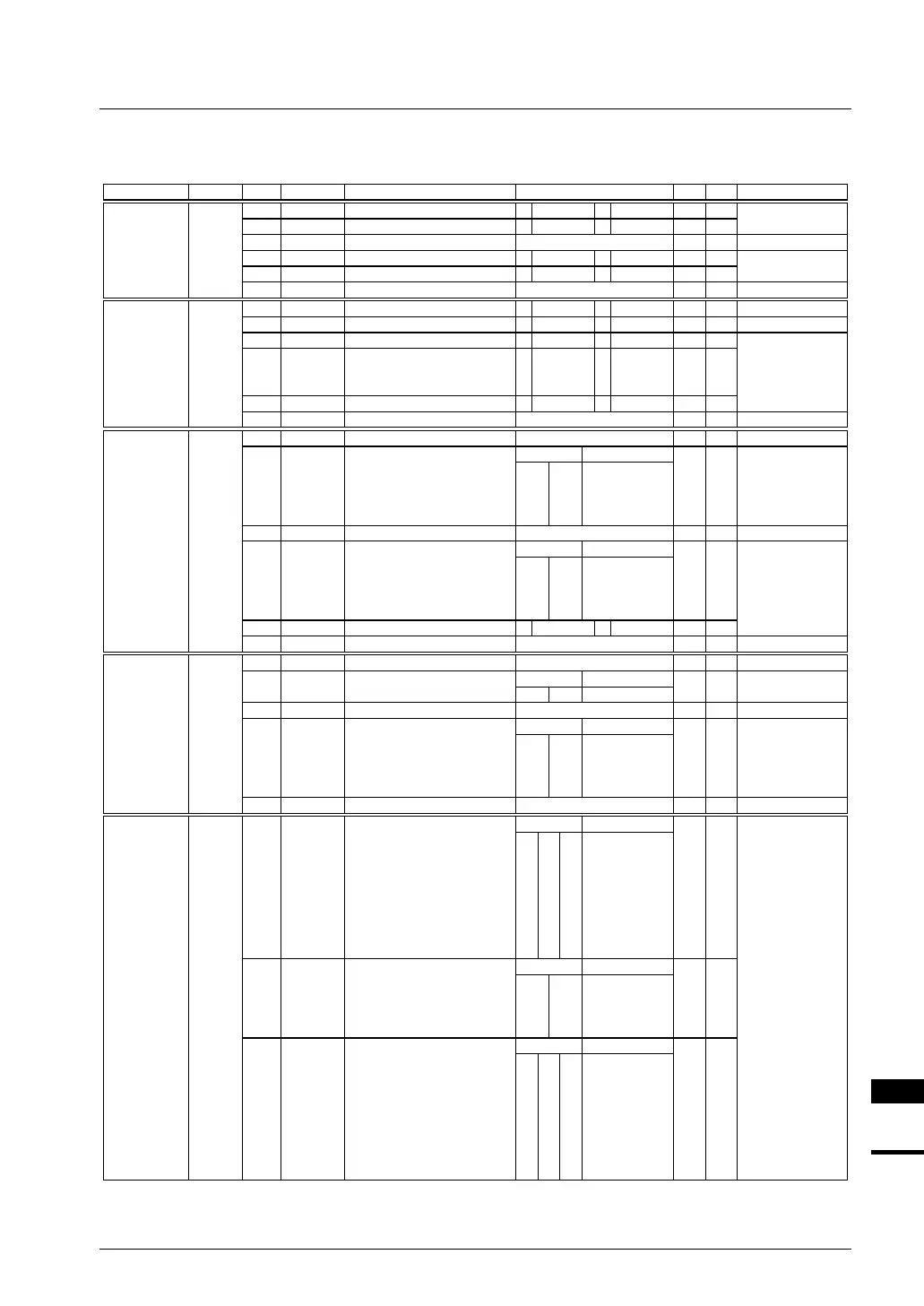

I/O Memory of SDRAM Interface

Table 2.12 shows the control bits of the SDRAM interface. These registers are mapped into area 6 (0x39FFC0 to

0x39FFCA).

Table 2.12 Control Bits of SDRAM Interface

NameAddressRegister name Bit Function Setting Init. R/W Remarks

–

–

SDRAR0

SDRAR1

–

SDRPC0

SDRPC1

–

D7

D6

D5–4

D3

D2

D1–0

Area 7/13 configuration

Area 8/14 configuration

reserved

#CE7/13 pin configuration

#CE8/14 pin configuration

reserved

0

0

–

0

0

–

R/W

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

039FFC0

(B)

1 SDRAM 0

Not SDRAM

1 SDRAM 0

Not SDRAM

1 #SDCE0 0 #CE7/13

1 #SDCE1 0 #CE8/14

SDRAM area

configuration

register

–

SDRENA

SDRINI

SDRSRF

SDRIS

SDRCLK

–

D7

D6

D5

D4

D3

D2–0

Enable SDRAM signals

Start SDRAM power up

Enable SDRAM self-refresh

Initial command sequence

Keep SDCLK during self-refresh

reserved

0

0

0

0

1

–

R/W

R/W

R/W

R/W

R/W

–

0 when being read.

0 when being read.

039FFC1

(B)

1 Enabled 0 Disabled

1 Start 0 –

1 1 precharge

2 set reg.

3 refresh

0 1 precharge

2 refresh

3 set reg.

1 Enabled 0 Disabled

1 Kept 0 Stopped

SDRAM

control register

–

–

––

SDRCA1

SDRCA0

–

SDRRA1

SDRRA0

SDRBA

–

D7

D6–5

D4

D3–2

D1

D0

reserved

SDRAM page size

(column range)

reserved

SDRAM row addressing range

Number of SDRAM banks

reserved

–

0

0

–

0

0

0

–

–

R/W

–

R/W

R/W

–

0 when being read.

0 when being read.

0 when being read.

039FFC2

(B)

1 4 banks 0 2 banks

SDRAM

address

configuration

register

1

1

0

0

1

0

1

0

SDRRA[1:0] Addressing range

reserved

8K (SDA[12:0])

4K (SDA[11:0])

2K (SDA[10:0])

1

1

0

0

1

0

1

0

SDRCA[1:0] Page size

reserved

1K (SDA[9:0])

512 (SDA[8:0])

256 (SDA[7:0])

–

–

––

SDRCL1

SDRCL0

–

SDRBL1

SDRBL0

–

D7

D6–5

D4

D3–2

D1–0

reserved

SDRAM CAS latency

reserved

SDRAM burst length

reserved

–

1

1

–

1

1

–

–

R/W

–

R/W

–

0 when being read.

0 when being read.

0 when being read.

039FFC3

(B)

SDRAM

mode set-up

register

1 0

SDRCL[1:0] CAS latency

2 CAS latency

1

1

0

0

1

0

1

0

SDRBL[1:0] Burst length

8

4

2

1

SDRTRAS2

SDRTRAS1

SDRTRAS0

SDRTRP1

SDRTRP0

SDRTRC2

SDRTRC1

SDRTRC0

D7–5

D4–3

D2–0

SDRAM t

RAS

spec

SDRAM t

RP

spec

SDRAM t

RC

spec

0

0

0

0

0

0

0

0

R/W

R/W

R/W

039FFC4

(B)

SDRAM

timing set-up

register 1

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

SDRTRAS[2:0]

Number of clocks

7

6

5

4

3

2

1

8

1

1

1

1

0

0

0

0

1

1

0

0

1

1

0

0

1

0

1

0

1

0

1

0

SDRTRC[2:0]

Number of clocks

7

6

5

4

3

2

1

8

1

1

0

0

1

0

1

0

SDRTRP[1:0]

Number of clocks

3

2

1

4

Loading...

Loading...