Chapter 2. IBM eX5 technology 27

on each of the attached memory buffers), DIMMs must be installed in quantities of four per

processor to enable Hemisphere Mode.

In addition, because eight DIMMs per processor are required for using all memory channels,

eight DIMMs per processor need to be installed at a time for optimized memory performance.

Failure to populate all eight channels on a processor can result in a performance reduction of

approximately 50%.

Hemisphere Mode does not require that the memory configuration of each CPU is identical.

For example, Hemisphere Mode is still enabled if CPU 0 is configured with 8x 4 GB DIMMs,

and processor 1 is configured with 8x 2 GB DIMMs. Depending on the application

characteristics, however, an unbalanced memory configuration can cause reduced

performance because it forces a larger number of remote memory requests over the

inter-CPU QPI links to the processors with more memory.

We summarize these points:

There are two memory buffers per memory channel, two channels per memory controller,

and two controllers per processor. Each memory channel must contain

at least one DIMM

to enable Hemisphere Mode.

Within a processor, both memory controllers need to contain identical DIMM

configurations to enable Hemisphere Mode. Therefore, for best results, install at least

eight DIMMs per processor.

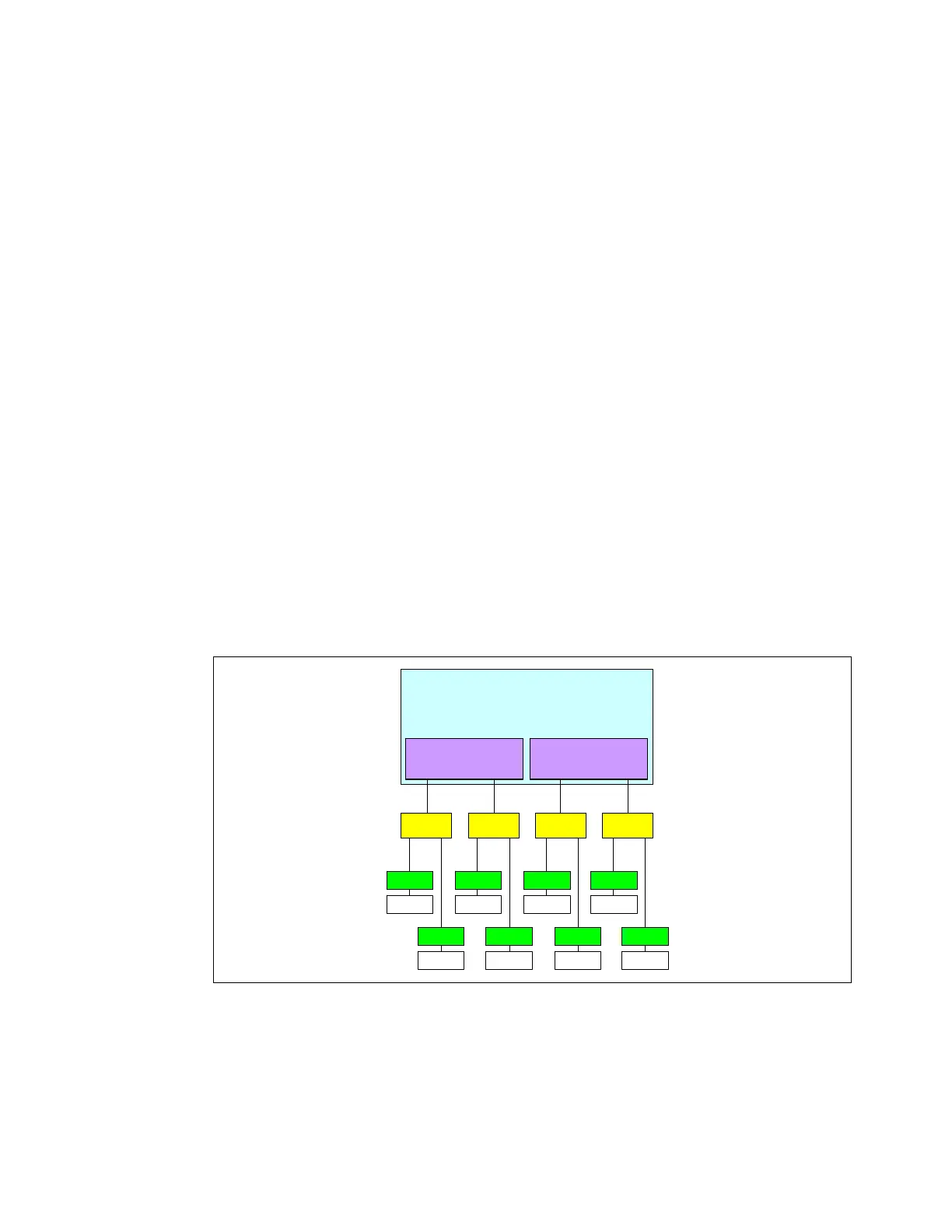

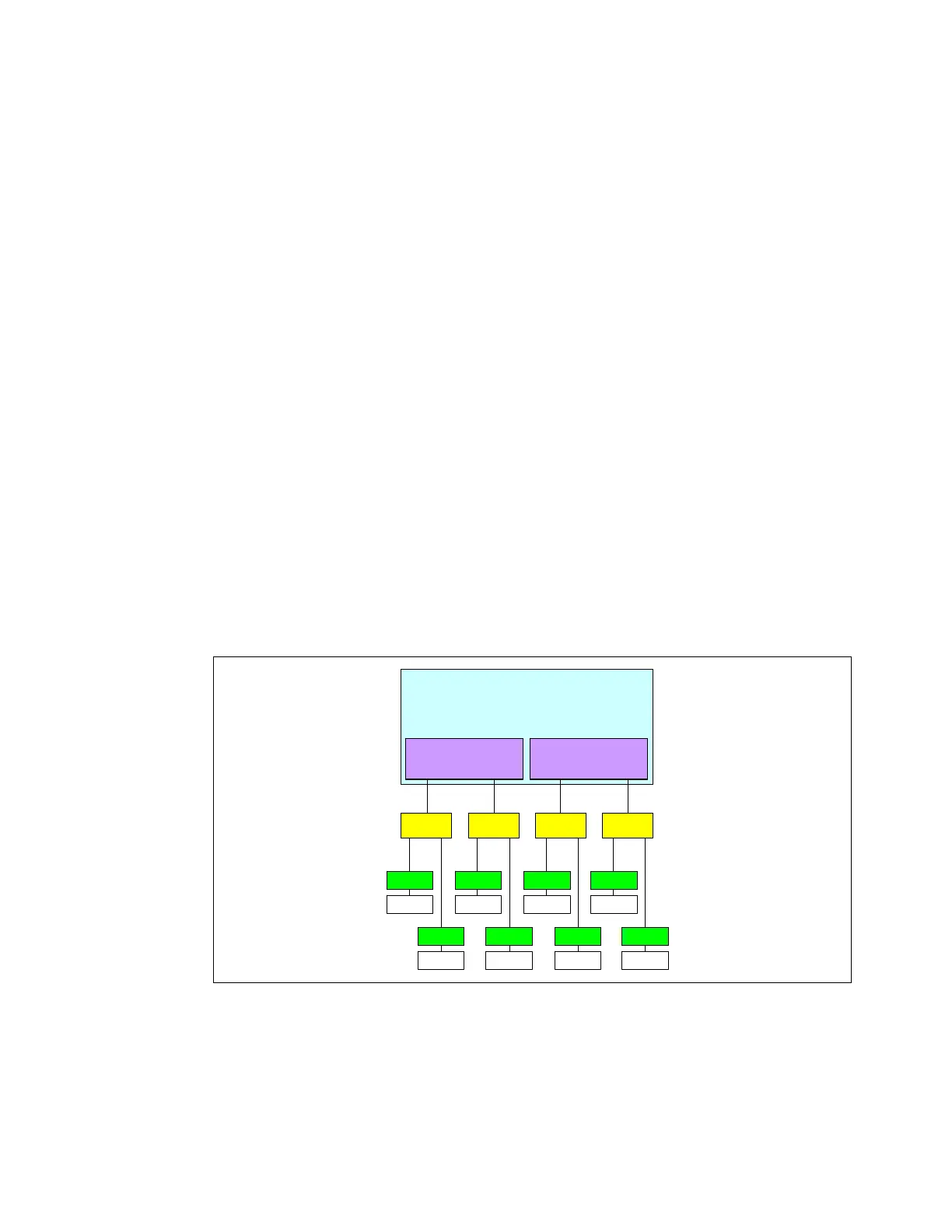

Industry-standard tests run on one Xeon 7500 processor with various memory configurations

have shown that there are performance implications if Hemisphere Mode is not enabled. For

example, for a configuration with eight DIMMs installed and spread across both memory

controllers in a processor and all memory buffers (see Figure 2-8), there is a drop in

performance of 16% if Hemisphere Mode is not enabled.

Figure 2-8 Example memory configuration

For more information about Hemisphere Mode installation options, see the following sections:

IBM System x3850 X5: 3.8.2, “DIMM population sequence” on page 79

IBM System x3690 X5: “Two processors with memory mezzanine installed” on page 135

IBM BladeCenter HX5: 5.10.2, “DIMM population order” on page 196

Intel Xeon 7500 processor

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMM

DIMMDIMM

Buffer Buffer Buffer Buffer

Memory

controller

Memory

controller

Loading...

Loading...