Chapter 3. IBM System Storage DS4000 and DS5000 hardware 35

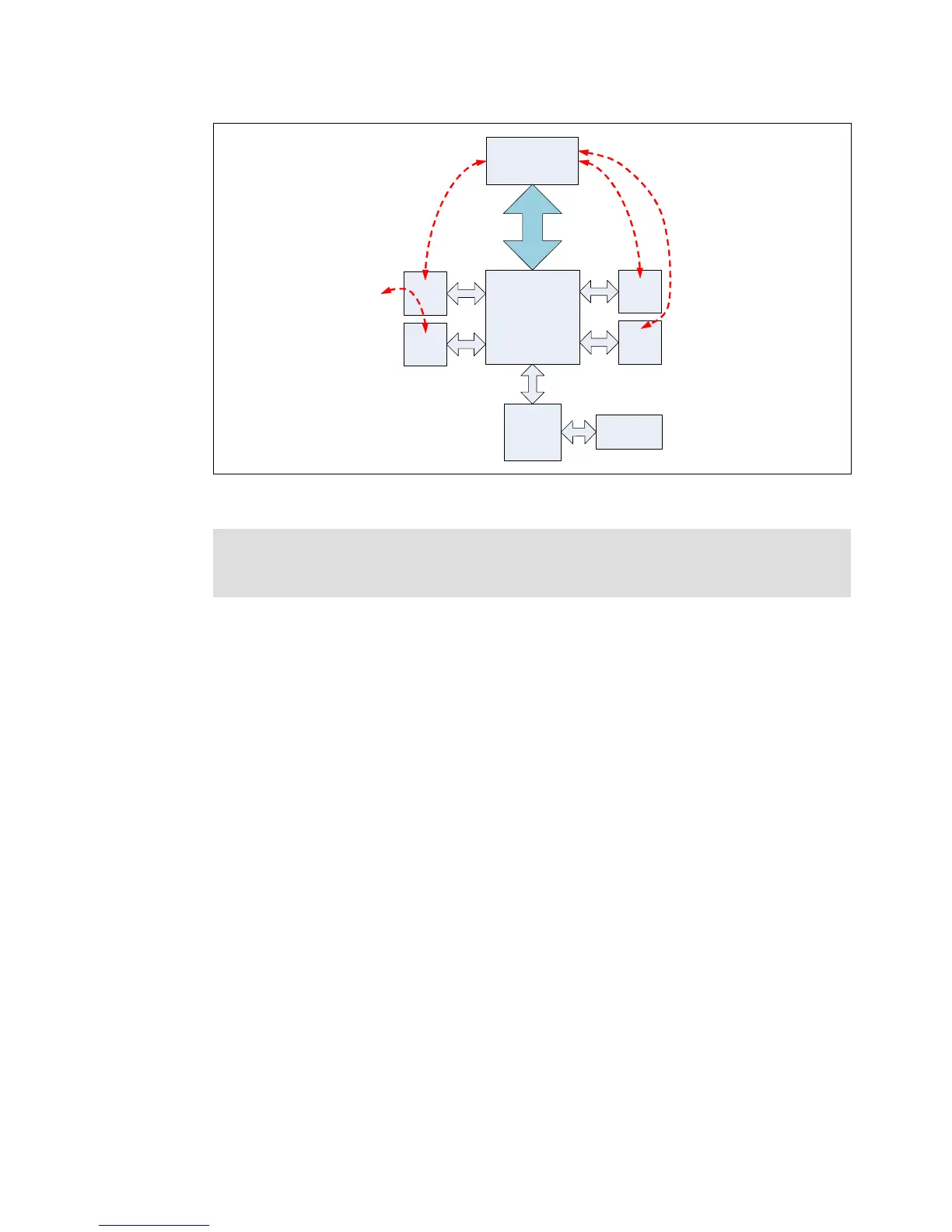

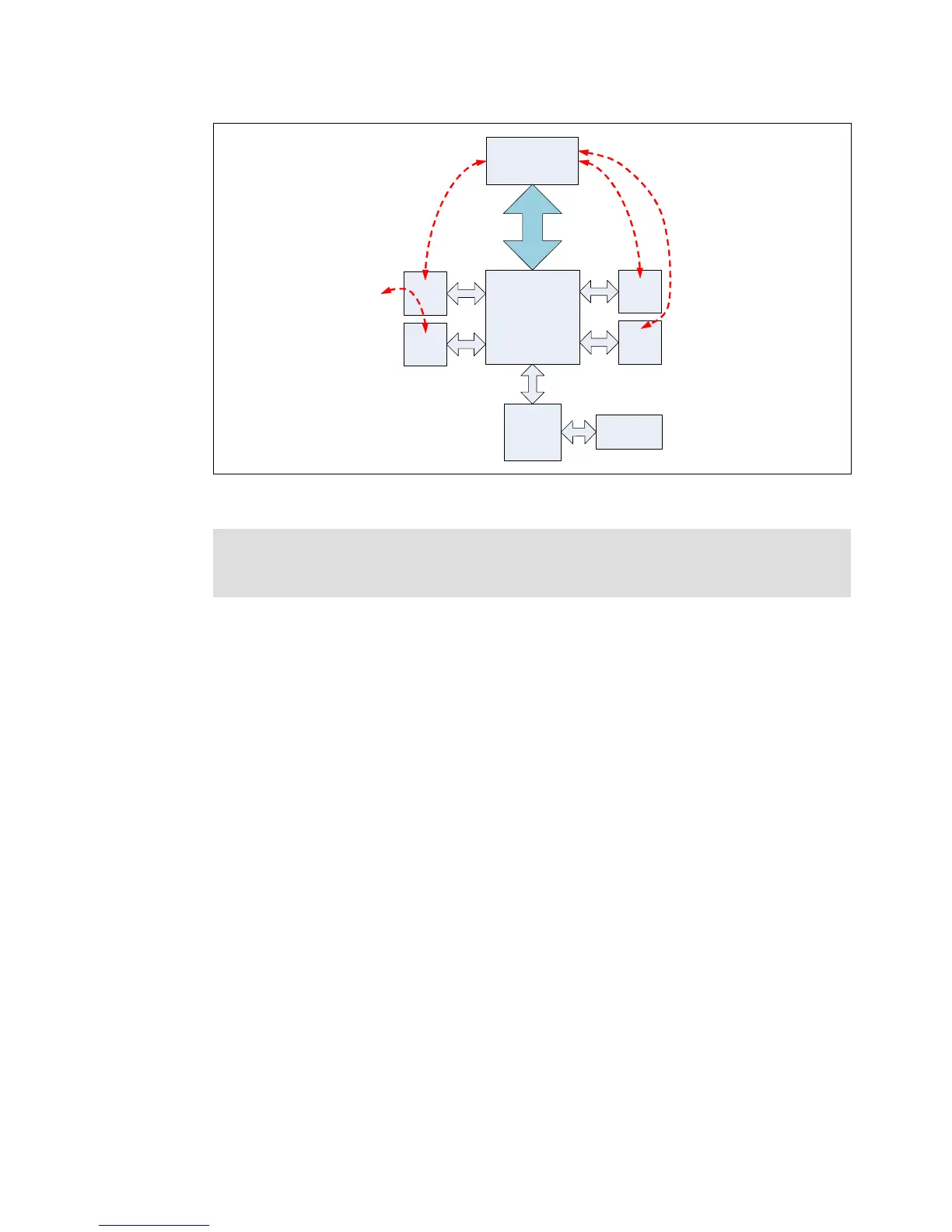

Figure 3-9 Cache memory access

The cache may have dirty data in it. The cache memory is RAM, so if there is a power failure,

the contents of the cache will be lost, including all the dirty data. There is no way for an

application using the storage subsystem to tell exactly how many writes were lost in a case

like this, so recovery can be very difficult or impossible. This severely limits the applicability of

write caching to non-essential data like scratch data, temporary files, and so on. To

circumvent this limitation, the controller can make the cache contents persist through power

failures by using persistent cache backup devices.

Persistent cache backup devices is a new method implemented in the DS5000 family. The

controller has persistent cache backup devices (USB flash memory) into which cache

contents can be stored for an indefinite period of time. In this case, the controller also has a

battery with enough capacity to let it write the full contents of the cache memory to the

persistent cache backup devices in case of a power failure. The controller firmware turns off

the batteries when the backup has been completed.

The state of the cache persistence mechanism is tied to the cache management subsystem

and affects write caching directly. If the cache persistence mechanism fails for some reason,

for example, the battery is missing in a battery-backed cache memory controller, write

caching will be disabled for all volumes, except those that have the “cache without batteries”

attribute set to true (see 4.10.6, “Cache parameters” on page 249 for more information).

Dirty data: A cache block that contains new data that is not consistent with data on disk is

dirty. The cache block holding the write data is dirty until the data is written to disk and the

cache block becomes clean.

Cache Memory

DDR2

ZIP

ASIC

1

7G

B

/

s

I/F

Host

I/F

Host

I/F

Host

I/F

PCIe PCIe

Intel

Xeon

Processor

memory

PCIe

D

M

A

D

M

A

Host

Loading...

Loading...