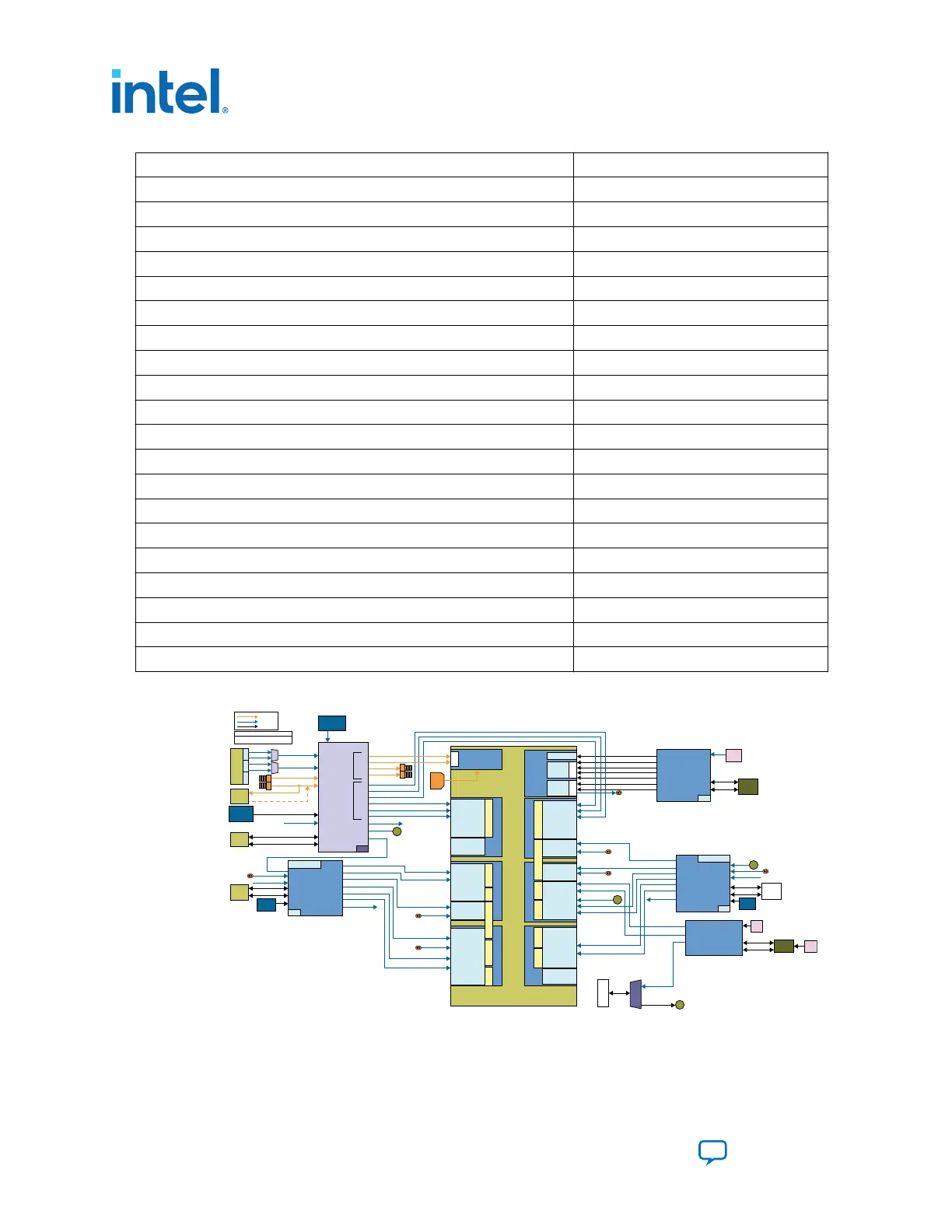

Schematic Signal Name Default Frequency (Hz)

REFCLK2_PCIE_100M_DP/DN 100M

REFCLK1_PCIE_100M_DP/N 100M

SI52204_CLKIN 25M

SI5391_XA 48M

CLK_FHT_13B_156.25M_DP/DN 156.25M

CLK_FHT_13C_156.25M_DP/DN 156.25M

CLK_FGT_13B_156.25M_DP/DN 156.25M

CLK_FGT_13B_156.25M_SPARE_DP/DN 156.25M

CLK_FGT_13A_156.25M_DP/DN 156.25M

CLK_FGT_13A_156.25M_SPARE_DP/DN 156.25M

CLK_SI5395_1_OUT9A_DP/DN 100M

CLKGEN_SI5395_2_XA 48M

CLK_FHT_12B_156.25M_DP/DN 156.25M

CLK_FHT_12C_156.25M_DP/DN 156.25M

CLK_FGT_12C_156.25M_DP/DN 156.25M

CLK_FGT_12C_156.25M_SPARE_DP/DN 156.25M

CLK_FGT_12B_156.25M_DP/DN 156.25M

CLK_FGT_12B_156.25M_SPARE_DP/DN 156.25M

CLK_SI5395_2_OUT9A_DP/DN 100M

FX2_XTALIN 24M

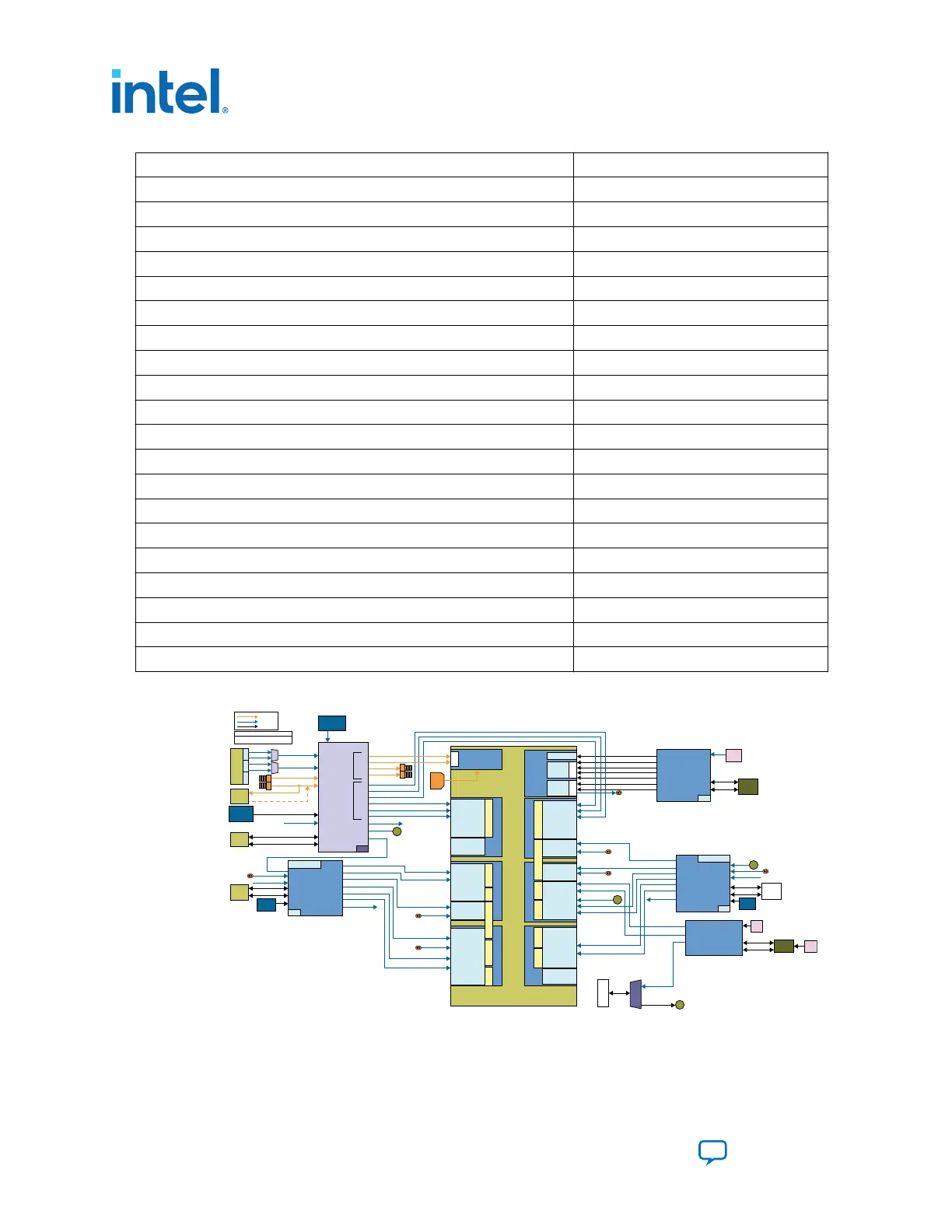

Figure 31. Clock Tree

12A

FGT

12A

MUX MUX

13C IOPLL

REFCLK-2 [GC]

REFCLK-4 [GC]

REFCLK-0

REFCLK-1

REFCLK-3 [GC]

FHT

FGT FGTFHT FHT

FMC+_A

12B

IOPLL

FGT

REFCLK-2 [GC]

ToD

REFCLK-0

REFCLK-1

REFCLK-3 [GC]

FHT

QSFPDD x8

QSFP

12C

13C 13B 13A

FGT

REFCLK-0

REFCLK-2 [GC]

REFCLK-3 [GC]

REFCLK-5 [GC]

REFCLK-4 [GC]

REFCLK-2 [GC]

REFCLK-1 [GC]

REFCLK-0 [GC]

REFCLK-2 [GC]

REFCLK-3 [GC]

REFCLK-4 [GC]

REFCLK-1

QSFP 28 x4

REFCLK-0

REFCLK-1

iobank_clk

iobank_clk

sdm_config_clk_125m

ddr4_bank1_clk

ddr4_bank2_clk

ddr4_bank3_clk

ddr4_bank4_clk

REFCLK-0

156.25M

156.25M

156.25M-SPARE

156.25M-SPARE

MCIO

SPDT MUX

REFCLK

rp_refout

OUT-3

OUT-2

OUT-1

OUT-0

External FB 2

External FB 2

External FB 1

External_FB_1

External_FB_1

SMA

SMA

FM91

OSCin

OSC

XTAL

48 MHz

25M

BMC

I2C/SPI

CTRL/STAT

pcie_ep_refin

156.25M

156.25M-SPARE

156.25M

156.25M-SPARE

156.25M

156.25M

156.25M

SMA

156.25M

pcie_ep_refin

Si52204

PCIe SRIS

pcie_rp_refclk1_100m

pcie_rp_refclk2_100m

REFCLK-1

FHT

QSFPDD x8

Intel Agilex 7 FPGA I-Series AGIC040R39A

SDM

DDR

Banks

IO

Banks

OSC

50M

BMC

OUT-8

CTRL/STAT

I2C/SPI

OUT-6

OUT-7

OUT-4

OUT-3

OUT-2

OUT-1

OUT-0A

Si5391

B

A

B

XTAL

48 MHz

SMA

SMA

1PPS_PLL_FB

tod_clk_10m

1pps_clk_fm91

1pps_out_sma

10m_out_sma

fmcb_cpri_refclk_184.32m

fmcb_cpri_refclk_153.6m

fmcb_eth_refclk_156.25m

fmca_eth_refclk_156.25m

fmca_cpri_refclk_153.6m

fmca_cpri_refclk_184.32m

1pps_pll_fb

48 MHz

FM91

FM91

FM91

TCXO/XO

XTAL

TCXO

19.44 MHz

7N19471003

1PPS_SMA_OUT

*OCXO OH19470001 with SAME FP

1PPS_SMA_IN

REFCLK9

REFCLK8

REFCLK9

REFCLK8

PTP Clocks

XX_CLK

NOTE:

Recovered Clock from banks:

o_clk_rec_div = 390.625M for aI 25G/10G modes

XX_CLK

XX_CLK

SyncE Clocks

Local Clocks

10MHz_SMA_IN

FMCB_RECRD_CLK

FMCA_RECRD_CLK

A

FMC+_B QSFP x8 PCIe x4

QSFP DD x8

QSFP DD x8 QSFP 28 x4

QSFP-DD 800 x8

QSFP28x4

IOPLLIOPLL

FM91

QSFPDD x8

FHTFGT

REFCLK-2 [GC]

REFCLK-3 [GC]

NVM

OUT-9

OUT-6

OUT-5

OUT-4

OUT-3

OUT-0

OUT-1

IN-0

IN-1

IN-3

I2C/SPI

CTRL/STAT

XA/XB

Si5395

Integrated RefIN

NVM

OUT-6

OUT-5

OUT-0

OUT-1

OUT-3

OUT-4

OUT-9

IN-0

IN-1

IN-3

I2C/SPI

CTRL/STAT

XA/XB

Si5395

Integrated RefIN

NVM

ToD

UART

OUT12

OUT14

OUT2

OUT6

OUT3

OUT0

OUT1

SyncE1588 PTP

OUT4

OUT7

OUT11

OUT10

OUT9

OUT8

NVM

Si5518

REF

IN0

IN1

IN2p

IN2n

IN3n

IN3p

I2C/SPI

CTRL/STAT

A. Development Kit Components

776646 | 2023.05.31

Intel Agilex

®

7 FPGA I-Series Transceiver (6 × F-Tile) Development Kit User

Guide

Send Feedback

40

Loading...

Loading...