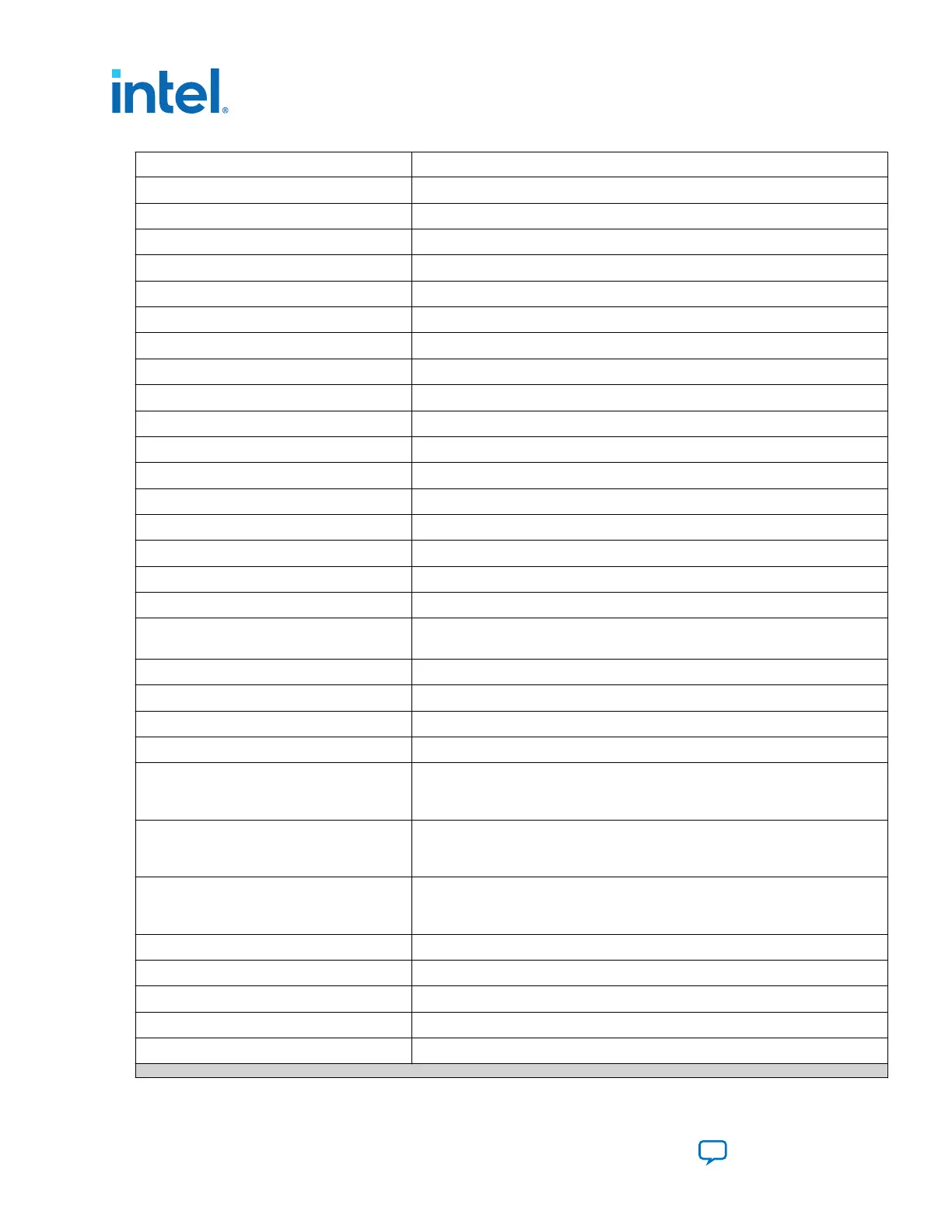

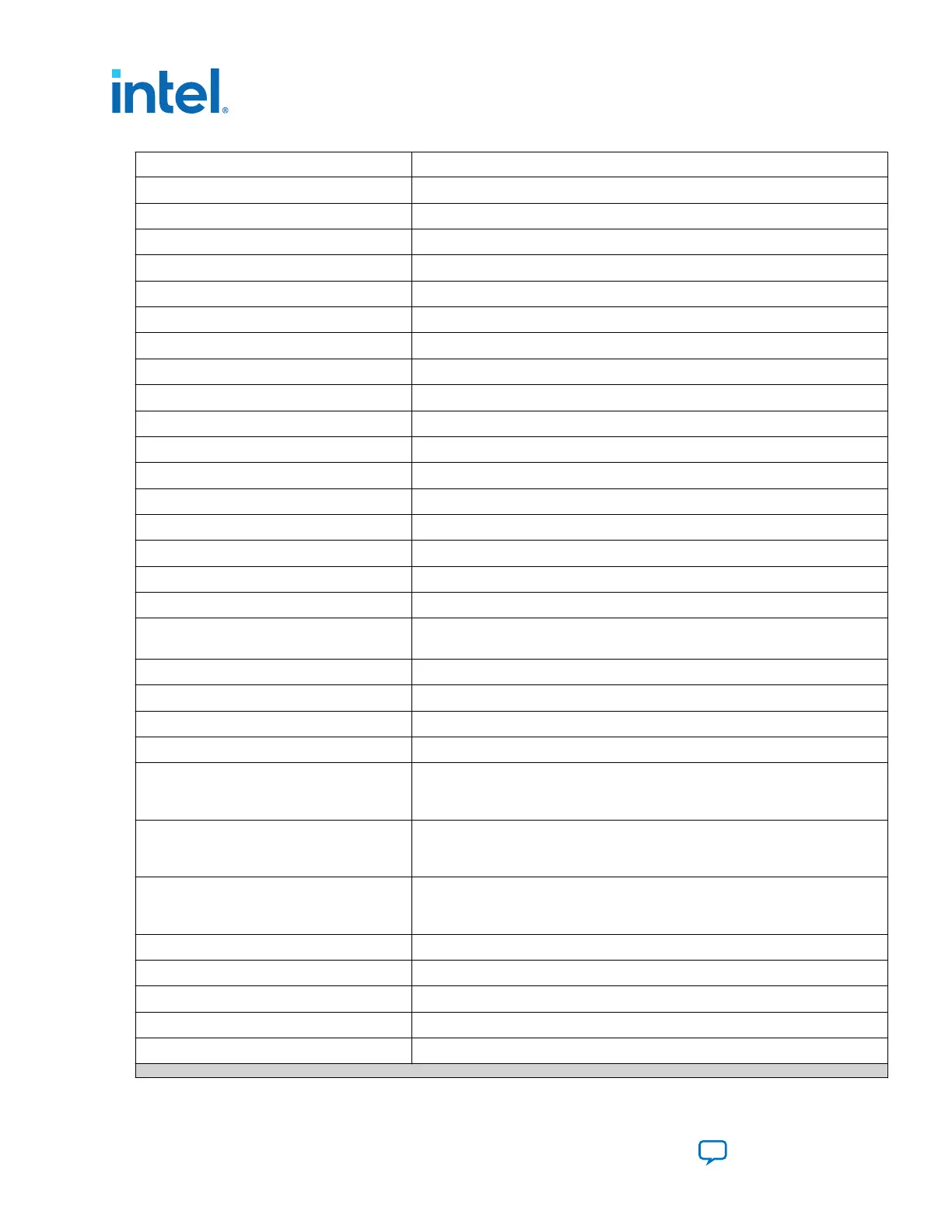

Schematic Signal Name Description

USER_LED3

User LED

USER_LED4

User LED

USER_LED5

User LED

USER_LED6

User LED

USER_LED7

User LED

F_GPIO0 The value of filtered user_pb[0]

F_GPIO1 The value of filtered user_pb[1]

F_GPIO2

MCIO_PERST in RP Mode

F_GPIO3

FMC_A_PERST in RP Mode

F_GPIO4

FMC_B_PERST in RP Mode

F_GPIO5

Reserved

F_GPIO6

Reserved

F_GPIO7

Reserved

F_GPIO8

Reserved

F_GPIO9

Reserved

F_GPIO10

Reserved

F_GPIO11

Reserved

SYS_SW0

Factory load:

0—Load image from Page 0 of the QSPI

SYS_SW1

NU

SYS_SW2

NU

SYS_SW3

NU

SYS_SW4

NU

SYS_SW5

FMC-A PCIe RP/EP Select:

"0": RP

"1": EP

SYS_SW6

FMC-B PCIe RP/EP Select:

"0": RP

"1": EP

SYS_SW7

MCIO PCIe RP/EP Select:

"0": RP

"1": EP

SYS_LED0/D9

PGM_LED0 for Avalon

®

-ST (AVST) configuration

SYS_LED2/D11

PGM_LED1 for AVST configuration

SYS_LED4/D13

PGM_LED2 for AVST configuration

SYS_LED6/D15

MAX_ERROR for AVST configuration

SYS_LED1/D10

MAX_LOAD for AVST configuration

continued...

A. Development Kit Components

776646 | 2023.05.31

Intel Agilex

®

7 FPGA I-Series Transceiver (6 × F-Tile) Development Kit User

Guide

Send Feedback

42

Loading...

Loading...