46

ECP5 and ECP5-5G High-Speed I/O Interface

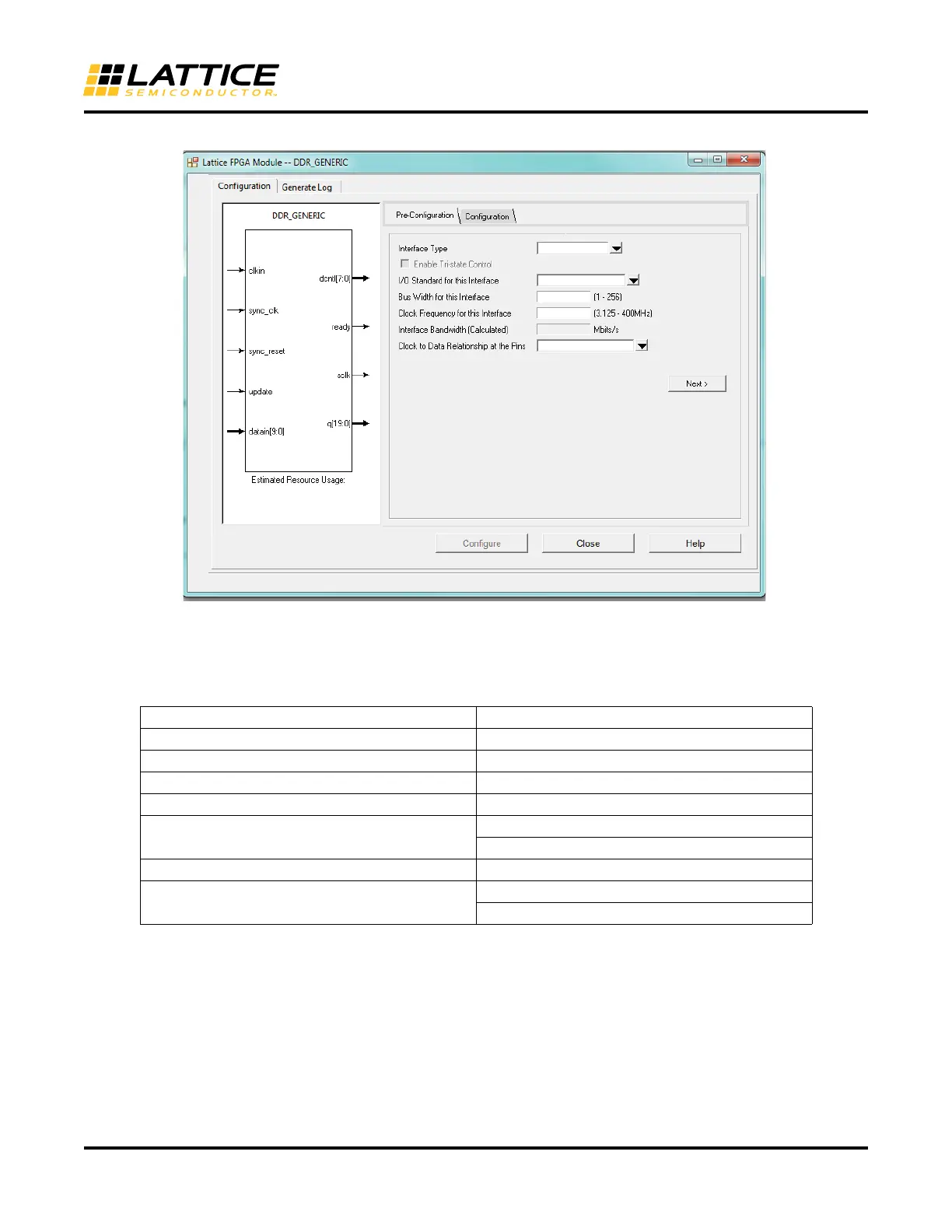

Figure 42. DDR_Generic Pre-Configuration Tab

Figure 42 shows the Pre-Configuration Tab for DDR generic interfaces. The Table 7 explains the various parame-

ters in this tab.

Table 7. DDR_Generic Pre-Configuration Parameters

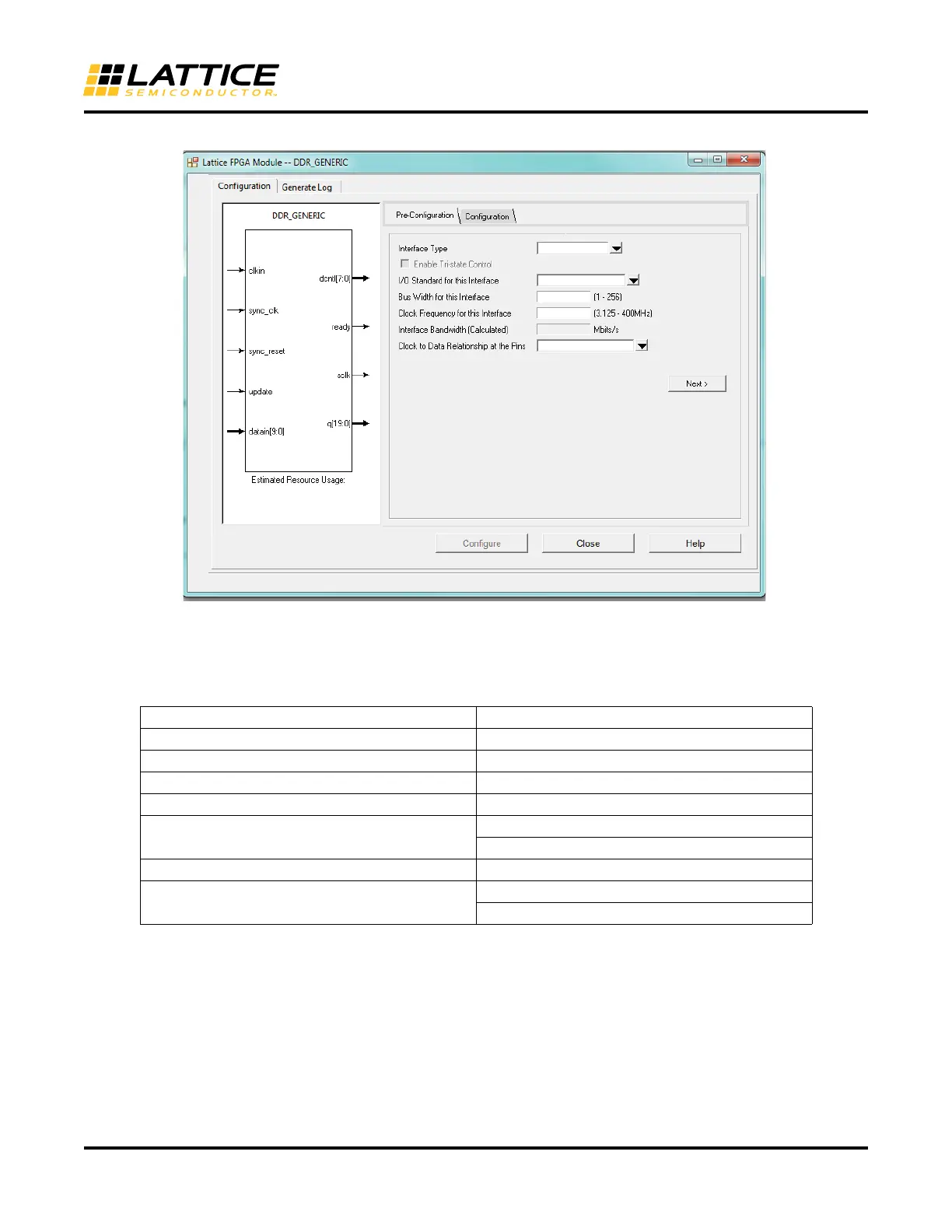

Based on the selections made in the Pre-Configuration Tab, the Configuration Tab is populated with the selections.

Figure 43 shows the Configuration Tab for the selection made in Pre-Configuration Tab.

GUI Option Range

Interface Type Transmit, Receive, Receive MIPI

I/O Standard for this Interface List of Legal Input or Output Standards

Enable Tristate Control Enabled, Disabled

Bus Width for this Interface 1 – 256

Clock Frequency for this Interface 3.125 – 400 MHz

200 – 400 MHz ( or Receive MIPI)

Interface Bandwidth (Calculated) Clock Frequency for * 2 * Bus Width

Clock to Data Relationship at the Pins Edge-to-Edge, Centered

Centered (for Receive MIPI)

Loading...

Loading...