53

ECP5 and ECP5-5G High-Speed I/O Interface

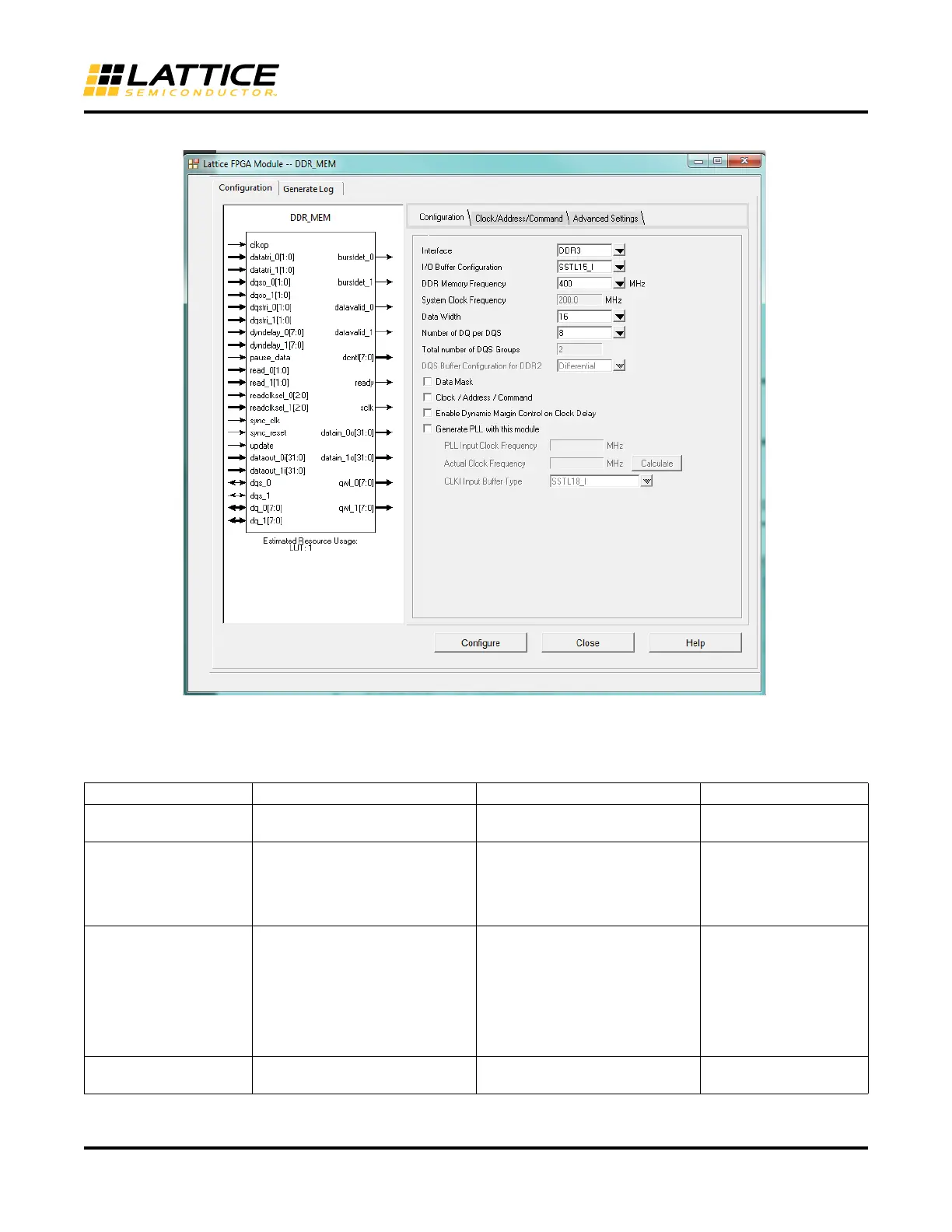

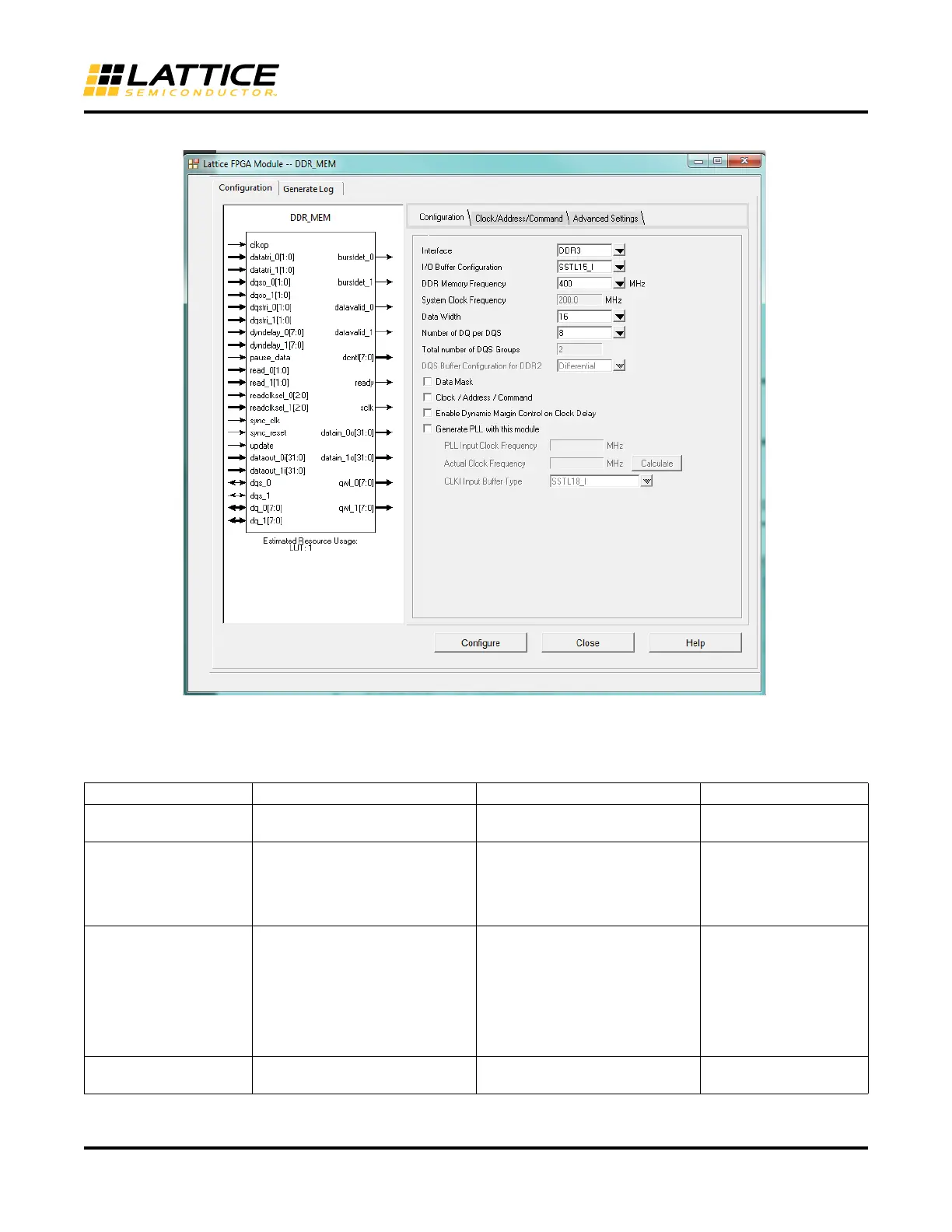

Figure 47. DDR_MEM Configuration Tab

Table 11 below describes the various settings shown in the Configuration tab.

Table 11. DDR_MEM Configuration Tab Parameters

GUI Option Description Range Default Value

Interface DDR memory interface type DDR2, DDR3, DDR3L, LPDDR2,

LPDDR3

DDR2

I/O Buffer Configuration I/O type configuration for DDR pins DDR2: SSTL18_I, STL18_II

DDR3: SSTL15_I, SSTL15_II

DDR3L: SSTL135_I, SSTL135_II

LPDDR2: HSUL12

LPDDR3: HSUL12

DDR2: SSTL18_I

DDR3: SSTL15_I

DDR3L: SSTL135_I

LPDDR2: HSUL2

LPDDR3: HSUL12

DDR Memory Frequency Target DDR memory interface fre-

quency

DDR2: 125, 200, 267, 333, 400

(MHz)

DDR3: 300, 400

DDR3L: 300, 400

LPDDR2: 125, 200, 267, 333, 400

(MHz)

LPDDR3: 125, 200, 267, 333, 400

(MHz)

DDR2: 267 MHz

DDR3: 400 MHz

DDR3L: 400 MHz

LPDDR2: 400 MHz

LPDDR3: 400 MHz

System Clock Frequency Calculated system clock frequency.

Not user selectable, display only.

SCLK Frequency Value DDR Memory Fre-

quency/2

Loading...

Loading...