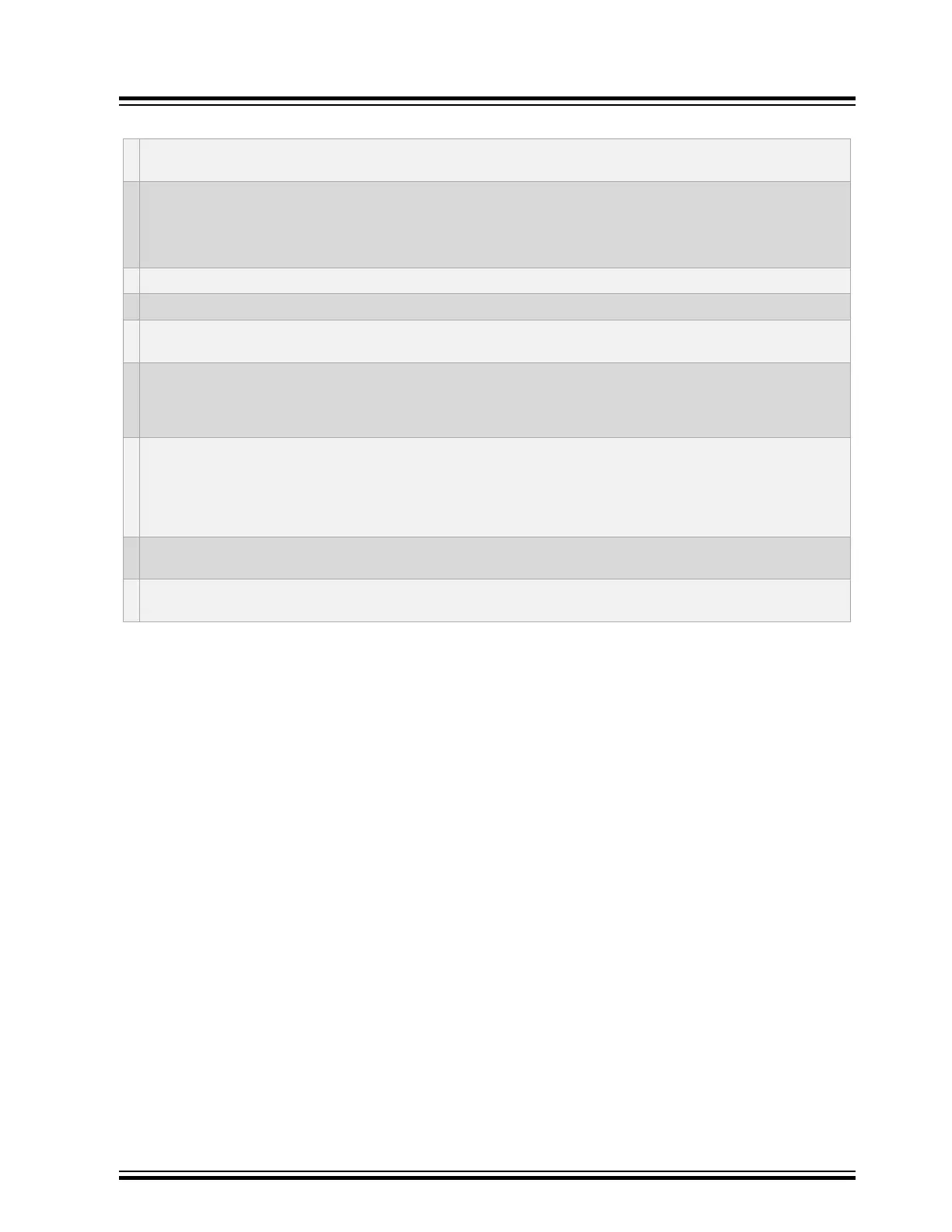

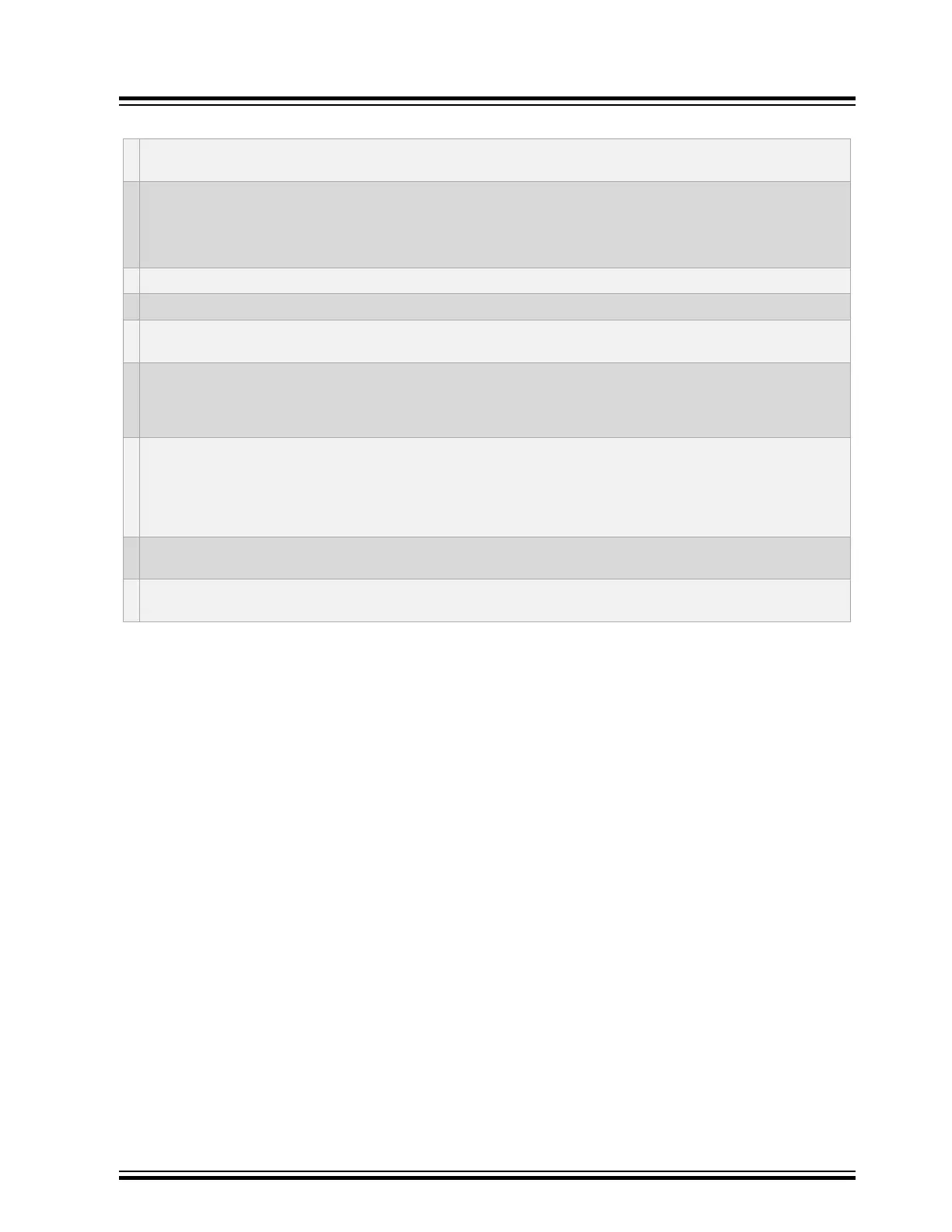

Table 11-5. USB PCB Layout Rules and Restrictions

1

Layout USB and USB differential traces first maintaining differential 90-ohm impedance matching on PCB layer 1, MCU component side,

adjacent to ground plane layer

.

2

D+ and D- PCB traces should not exceed:

1. USB High Speed = 3.5 inches, (88.9mm)

2. USB Full Speed = 4.5 inches, (114.3mm)

3. USB Low Speed = 6 inches, (152.4mm)

3 Ensure that D+ and D- traces have an unbroken reference ground plane with no ground gaps or voids beneath them.

4 Ensure that D+ and D- trace lengths are identical.

5

D+ and D- traces should not have any PCB via’s, (i.e. feedthrough holes), or sharp corners or they will disrupt the impedance at frequency

and cause reflections.

6

The USB connector shield should not be directly connected to the digital logic ground. Although differential signals offer good noise immunity,

they are susceptible to ground loops that can create offsets on the signal level thresholds. A capacitor between the USB shield and logic

ground is not a good design practice as it will conduct an ESD discharge directly into the MCU system. (See the USB design example

illustrations on the pages that follow.)

7

If using protection components:

1. Locate these immediately close to the USB PCB connector and do not use stubs. Components should be surface mounted in-line

with D+ and D- traces to maintain impedance matching and minimize reflections. If a stub is unavoidable, ensure it’s less than

200mils.

2. High Speed & Full Speed, USB, protection component load should not exceed 1.5pF per signal.

8

D+/D- traces should not have any extra components to maintain signal integrity. For example, traces should not be routed to multiple USB

connectors ideally.

9

Do not route USB traces under or near crystals, oscillators, clock signal generators, switching regulators, mounting holes, magnetic devices,

or IC’s that use or duplicate clock signals.

Note: Refer to the Complete PCB Layout Guidelines.

Serial Data Corruption Errors

© 2022 Microchip T

echnology Inc.

and its subsidiaries

Manual

DS70005439B-page 45

Loading...

Loading...