-----~-"--~

-----------------------

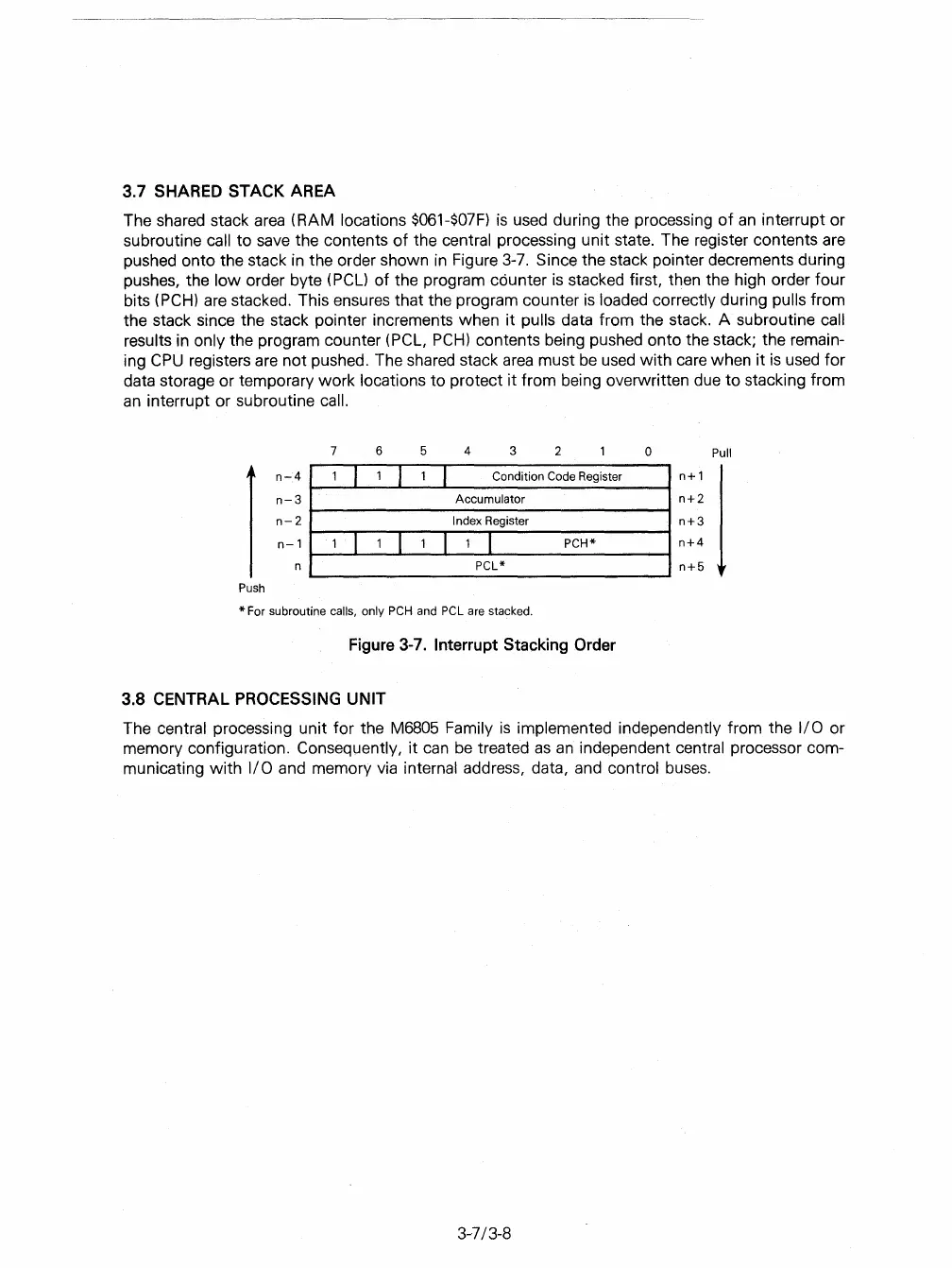

3.7 SHARED STACK AREA

The shared stack area (RAM locations $061-$07F)

is

used during the processing

of

an

interrupt

or

subroutine call

to

save the contents

of

the central processing unit state. The register contents are

pushed onto the stack in the order shown

in

Figure

3-7.

Since the stack pointer decrements during

pushes, the

low

order byte (PCL) of the program counter

is

stacked first, then the high order four

bits

(PCH) are stacked. This ensures that the program counter

is

loaded correctly during pulls from

the stack since the stack pointer increments when

it

pulls data from the stack. A subroutine call

results

in only the program counter

(PCl,

PCH)

contents being pushed onto the stack; the remain-

ing

CPU

registers are

not

pushed. The shared stack

area

must

be

used

with

care when

it

is

used

for

data storage or temporary

work

locations

to

protect

it

from being overwritten due

to

stacking from

an

interrupt

or

subroutine call.

I

Push

n-4

n-3

n-2

n-l

n

7

1

I

1

I

6 5

1

I

1

1

I

1

4

3

2

I

Condition Code Register

Accumulator

Index Register

I

1

I

PCH*

PCl*

* For subroutine calls, only

PCH

and

PCl

are stacked.

Figure 3-7. Interrupt Stacking Order

3.8 CENTRAL PROCESSING UNIT

o

Pull

:::

[

n+4

n+5

The central processing unit for the M6805 Family

is

implemented independently from the

110

or

memory configuration. Consequently,

it

can

be

treated

as

an

independent central processor com-

municating

with

1/0 and memory

via

internal address, data, and control buses.

3-7/3-8

Loading...

Loading...