Display

Jetson AGX Xavier Series Product DG-09840-001_v2.5 | 65

Module Pin Name Module Pin #s SoC Pin Name SoC Pin #s HDMI DP

HDMI_DP2_TX0_N D52 HDMI_DP2_TXDN0 G45 TXD2_N TXD0_N

HDMI_DP2_TX1_P

HDMI_DP2_TX1_N

B51

B52

HDMI_DP2_TXDP1

HDMI_DP2_TXDN1

F44

G44

TXD1_P

TXD1_N

TXD1_P

TXD1_N

HDMI_DP2_TX2_P

HDMI_DP2_TX2_N

A51

A50

HDMI_DP2_TXDP2

HDMI_DP2_TXDN2

H43

G43

TXD0_P

TXD0_N

TXD2_P

TXD2_N

HDMI_DP2_TX3_P

HDMI_DP2_TX3_N

C51

C50

HDMI_DP2_TXDP3

HDMI_DP2_TXDN3

G42

F42

TXC_P

TXC_N

TXD3_P

TXD3_N

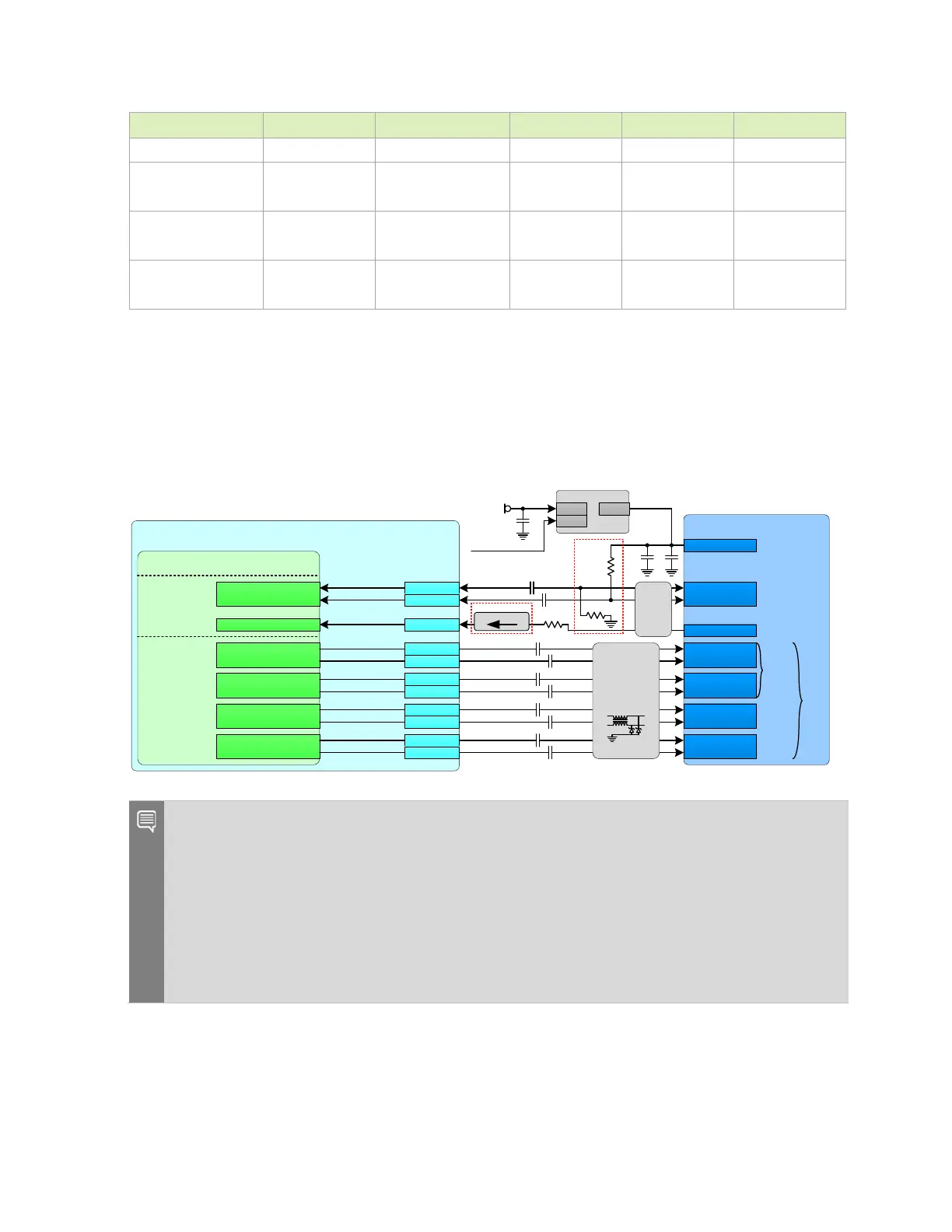

9.1 DP and eDP

Figure 9-1 shows the connection example for the DP and eDP connectors.

Figure 9-1. DP and eDP Connection Example

Jetson AGX Xavier

SoC

DPx_AUX_CH_P

DPx_AUX_CH_N

DPx_HPD

HDMI_DPx_TX0_P

HDMI_DPx_TX0_N

HDMI_DPx_TX1_P

HDMI_DPx_TX1_N

HDMI_DPx_TX2_P

HDMI_DPx_TX2_N

HDMI_DPx_TX3_P

HDMI_DPx_TX3_N

HDMI_DPx_TXDP0

HDMI_DPx_TXDN0

HDMI_DPx_TXDP1

HDMI_DPx_TXDN1

HDMI_DPx_TXDP2

HDMI_DPx_TXDN2

HDMI_DPx_TXDP3

HDMI_DPx_TXDN3

DP_AUX_CHx_P

DP_AUX_CHx_N

EDP

HDMI_DPx

DP_AUX_CHx_HPD

eDP / DP Connector

LN2+

LN2–

HPD

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

LN1+

LN1–

LN0+

LN0–

LN3+

LN3–

AUX+

AUX–

2-lan e

4-lan e

Lev el Shifte r

Se e Note 1

EMI/ESD

1kΩ

EMI/

ESD

10 0kΩ

10 0kΩ

0. 1uF 10uF

See

Note 2

+3.3V

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

F52/J52/G 53

DP0 /DP1/ DP2

F51/J53/G 54

H49/A47/D51

H48/A48/D52

G51/B49/B51

G50/B48/B52

J47/D49/A51

J48/D48/A50

K46/E50/C51

K47/E51/C50

K52/K51/K50

Load Switch

EN

IN OUT

VDD_3 V3

VDD_3V3_DP

VDD_3 V3 _PG OOD

Notes:

1. A Level shifter is required on HPD to avoid the pin from being driven when the module is off.

The level shifter must be non-inverting (preserve polarity of the signal from the display).

2. Pull-up/down only required for DP - not for eDP.

3. If EMI devices are necessary, they must be tuned to minimize the impact to signal quality,

which must meet the timing and electrical requirements of the DisplayPort specification for

the modes to be supported. Any ESD solution must also maintain signal integrity and meet the

DisplayPort requirements for the modes to be supported.

Loading...

Loading...