USB, PCIe, and UFS

Jetson AGX Xavier Series Product DG-09840-001_v2.5 | 50

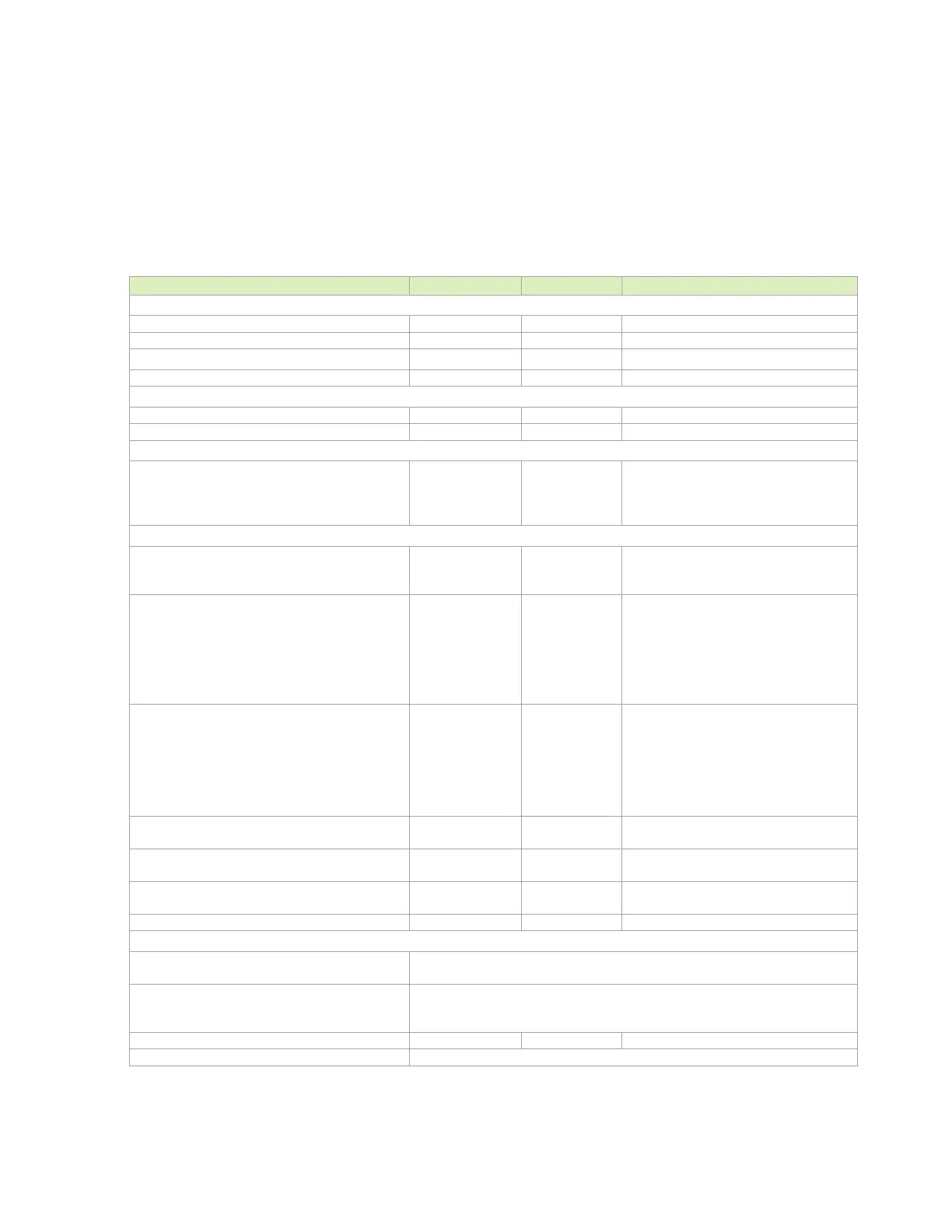

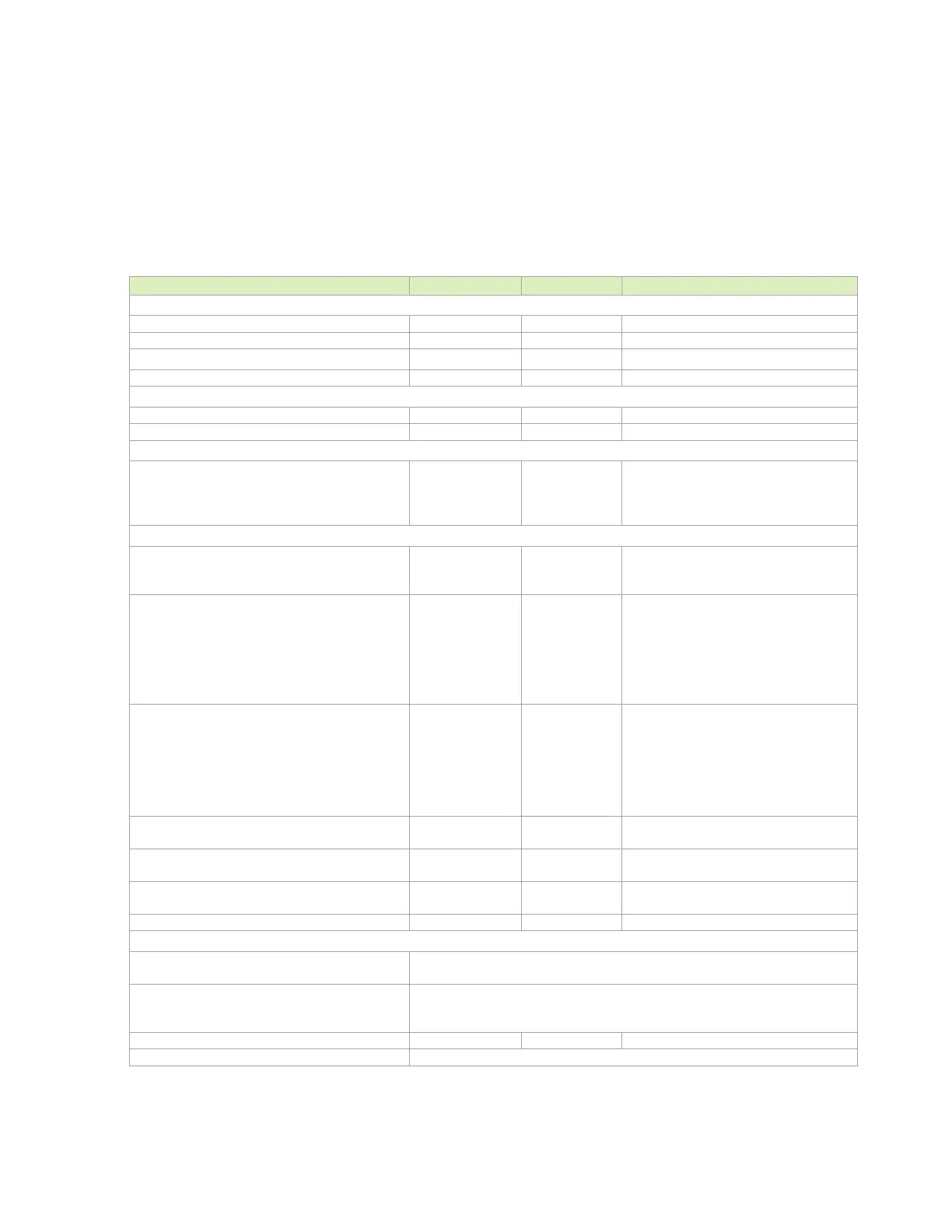

7.2.1 PCIe Design Guidelines up to Gen3

The following table details the PCIe design guidelines up to Gen3. See Section 7.2.2 for design

guidelines regarding PCIe Gen4.

Table 7-12. PCIe Interface Signal Routing Requirements up to Gen3

2.5GHz, half-rate architecture

Configuration / Device Organization

Unidirectional,

To GND Single Ended for P and N

Trace Impedance differential / Single Ended

Trace Spacing (Stripline/Microstrip)

Pair – Pair

To plane and capacitor pad

To unrelated high-speed signals

3x / 4x

3x / 4x

Dielectric

TX and RX should not be routed on the

same layer. See Note 2.

Breakout region (Max Length)

Minimum width and spacing. 4x or

wider dielectric height spacing is

Trace loss budget (for carrier board routing)

Routing direct to device

Routing to PCIe/M.2 connector

-14.5

-10.5

dB/in

@ 4GHz (See TBD),

Loss: GEN3 budget – module – end

device (-22dB + 3.5.dB + 4dB)

Loss: GEN3 budget – module – end

device (-28dB + 4.24dB + 8dB)

Max trace length (delay)

Direct to device on carrier board

Stripline

Microstrip

Routed to PCIe or M.2 connector

Stripline

491 (3383)

460 (27.19)

355 (2450)

in (ps)

Mid-loss PCB of 0.8dB/in (Microstrip) or

0.75dB/in (Stripline) is used. Also,

6.9ps/mm for Stripline routing and

5.9ps/mm for Microstrip.

Max PCB via distance from the BGA

Max distance from BGA ball to first PCB

via.

PCB within pair (intra-pair) skew

Do trace length matching before hitting

discontinuities

Within pair (intra-pair) matching between

subsequent discontinuities

Differential pair uncoupled length

Place GND vias as symmetrically as possible to data pair vias. GND via

distance should be placed less than 1x the diff pair via pitch

PTH Vias

2 for TX traces and 2 for RX trace

Longer via stubs would require review

Routing signals over antipads

Loading...

Loading...