Relion 1900e/2900e Manual

115 Revision 1.3

supplies must be able to load share in parallel and operate in a hot-swap/redundant 1+1 configurations.

The 12VSBoutput is not required to actively share current between power supplies (passive sharing). The

12VSBoutput of the power supplies are connected together in the system so that a failure or hot swap of a

redundant power supply does not cause these outputs to go out of regulation in the system.

13.2.14 Ripple/Noise

The maximum allowed ripple/noise output of the power supply is defined in the following table. This is

measured over a bandwidth of 10Hz to 20MHz at the power supply output connectors. A 10µF tantalum

capacitor in parallel with a 0.1µF ceramic capacitor is placed at the point of measurement.

Table 55. Ripples and Noise

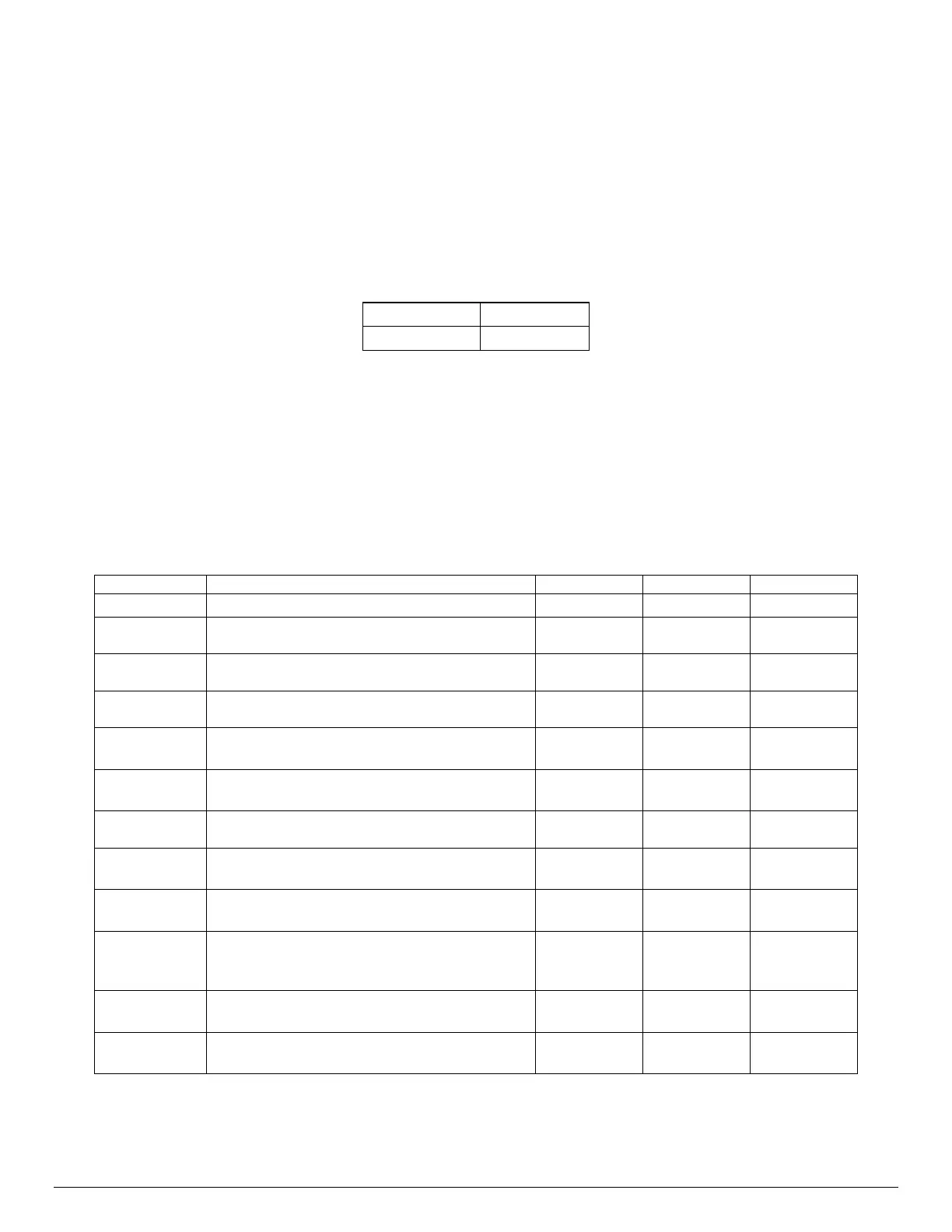

13.2.15 Timing Requirements

These are the timing requirements for the power supply operation. The output voltages must rise from 10%

to within regulation limits (T

vout_rise

) within 5 to 70ms. For 12VSB, it is allowed to rise from 1.0 to 25ms. All

outputs must rise monotonically. The following table shows the timing requirements for the power supply

being turned on and off from the AC input, with PSON held low and the PSON signal, with the AC input

applied.

Table 56. Timing Requirements

vout_rise

Delay from AC being applied to 12VSBbeing

within regulation.

Delay from AC being applied to all output

voltages being within regulation.

Time 12Vl output voltage stay within regulation

after loss of AC.

p

Delay from loss of AC to de-assertion of PWOK

ay

Delay from PSON# active to output voltages

within regulation limits.

Delay from PSON# deactivate to PWOK being

de-asserted.

Delay from output voltages within regulation

limits to PWOK asserted at turn on.

Delay from PWOK de-asserted to output

voltages dropping out of regulation limits.

Duration of PWOK being in the de-asserted state

during an off/on cycle using AC or the PSON

signal.

Delay from 12VSBbeing in regulation to O/Ps

being in regulation at AC turn on.

p

Time the 12VSBoutput voltage stays within

regulation after loss of AC.

* The

12VSBoutput voltage rise time shall be from 1.0ms to 25ms

Loading...

Loading...