Relion 1900e/2900e Manual

Revision 1.3 146

TPM device failed self test.

PCI component encountered a SERR error

PCI express* component encountered a PERR error

PCI express* component encountered an SERR error

DXE Boot Services driver: Not enough memory available to shadow a Legacy Option ROM.

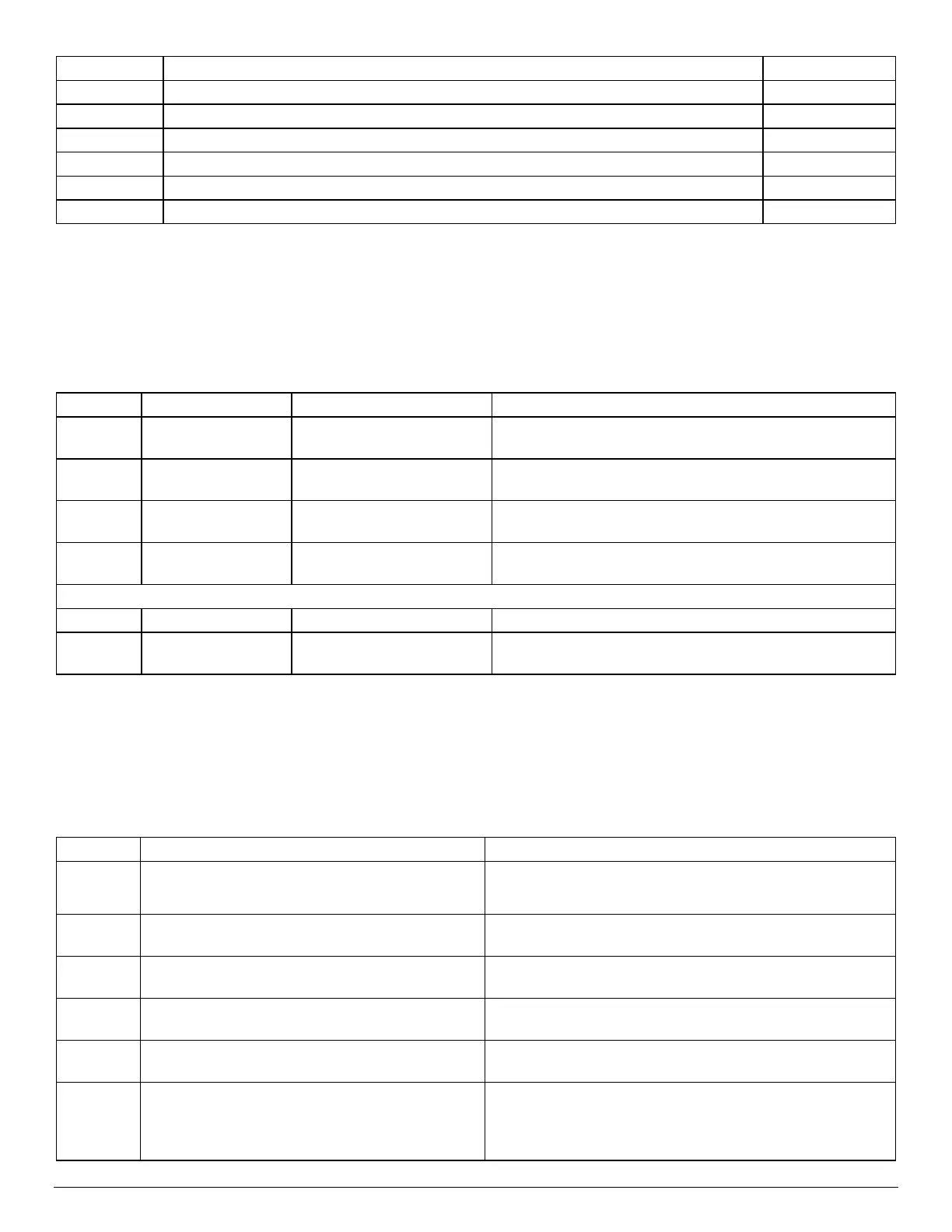

POST Error Beep Codes

The following table lists the POST error beep codes. Prior to system video initialization, the BIOS uses these

beep codes to inform users on error conditions. The beep code is followed by a user-visible code on the

POST Progress LEDs.

Table 65. POST Error Beep Codes

Short beep sounded whenever USB device is discovered in

POST, or inserted or removed during runtime.

violation

System halted because Intel® Trusted Execution Technology

detected a potential violation of system security.

System halted because a fatal error related to the memory

was detected.

1

System halted because a fatal error related to the CPU

family/core/cache mismatch was detected.

The following Beep Codes are sounded during BIOS Recovery.

Recovery boot has been initiated.

Recovery has failed. This typically happens so quickly after

recovery is initiated that it sounds like a 2-4 beep code.

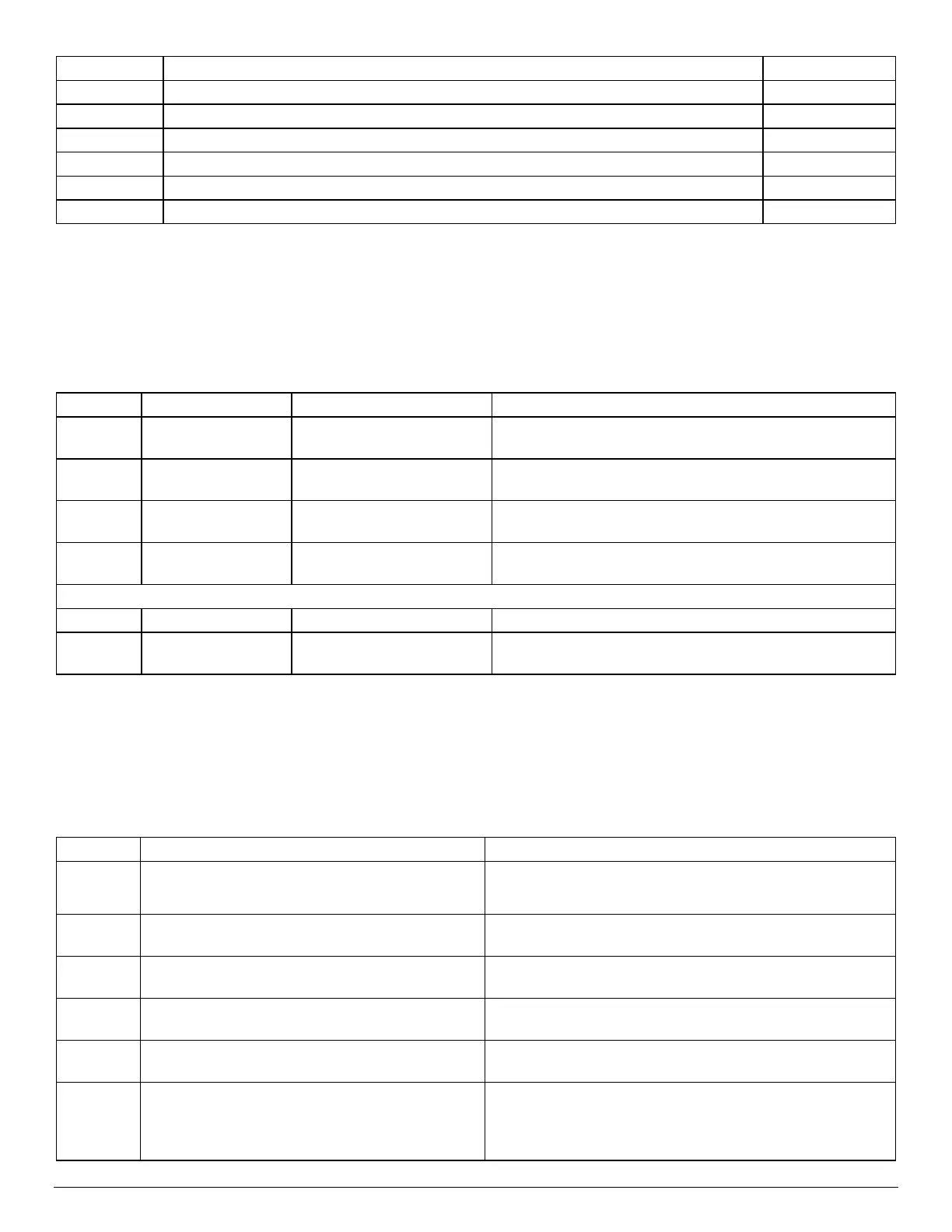

The In

tegrated BMC may generate beep codes upon detection of failure conditions. Beep codes are sounded

each time the problem is discovered, such as on each power-up attempt, but are not sounded continuously.

Codes that are common across all Intel server boards and systems that use same generation chipset are

listed in the following table. Each digit in the code is represented by a sequence of beeps whose count is

equal to the digit.

Table 66. Integrated BMC Beep Codes

No CPUs installed or first CPU socket is empty.

CPU1 socket is empty, or sockets are populated incorrectly

CPU1 must be populated before CPU2.

MSID mismatch occurs if a processor is installed into a system

board that has incompatible power capabilities.

DC power unexpectedly lost (power good dropout) – Power

unit sensors report power unit failure offset

Power control fault (power good assertion timeout).

Power good assertion timeout – Power unit sensors report soft

power control failure offset

VR Watchdog Timer sensor assertion

VR controller DC power on sequence was not completed in

time.

The system does not power on or unexpectedly powers off

and a Power Supply Unit (PSU) is present that is an

incompatible model with one or more other PSUs in the

system.

Loading...

Loading...