MC9S08QE128 MCU Series Reference Manual, Rev. 2

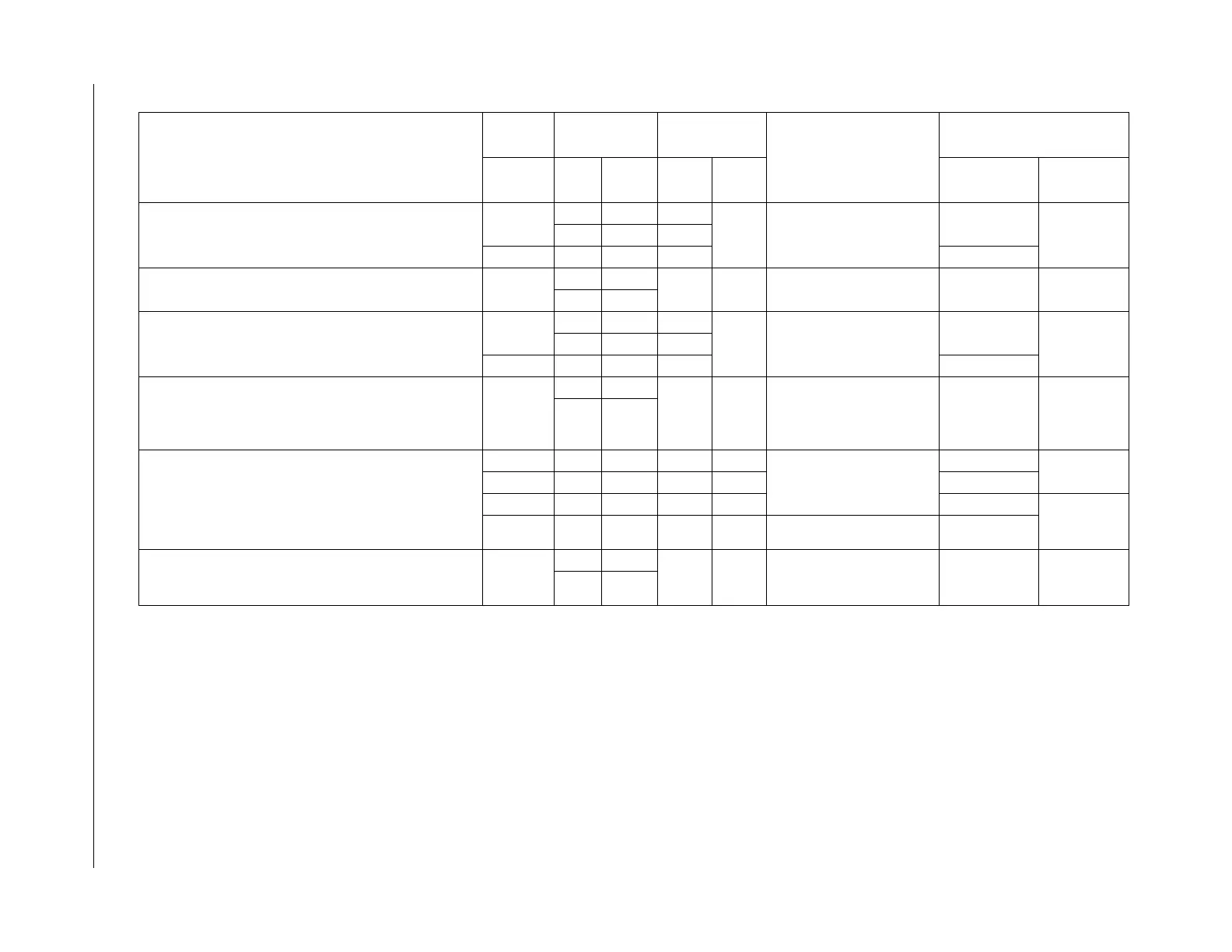

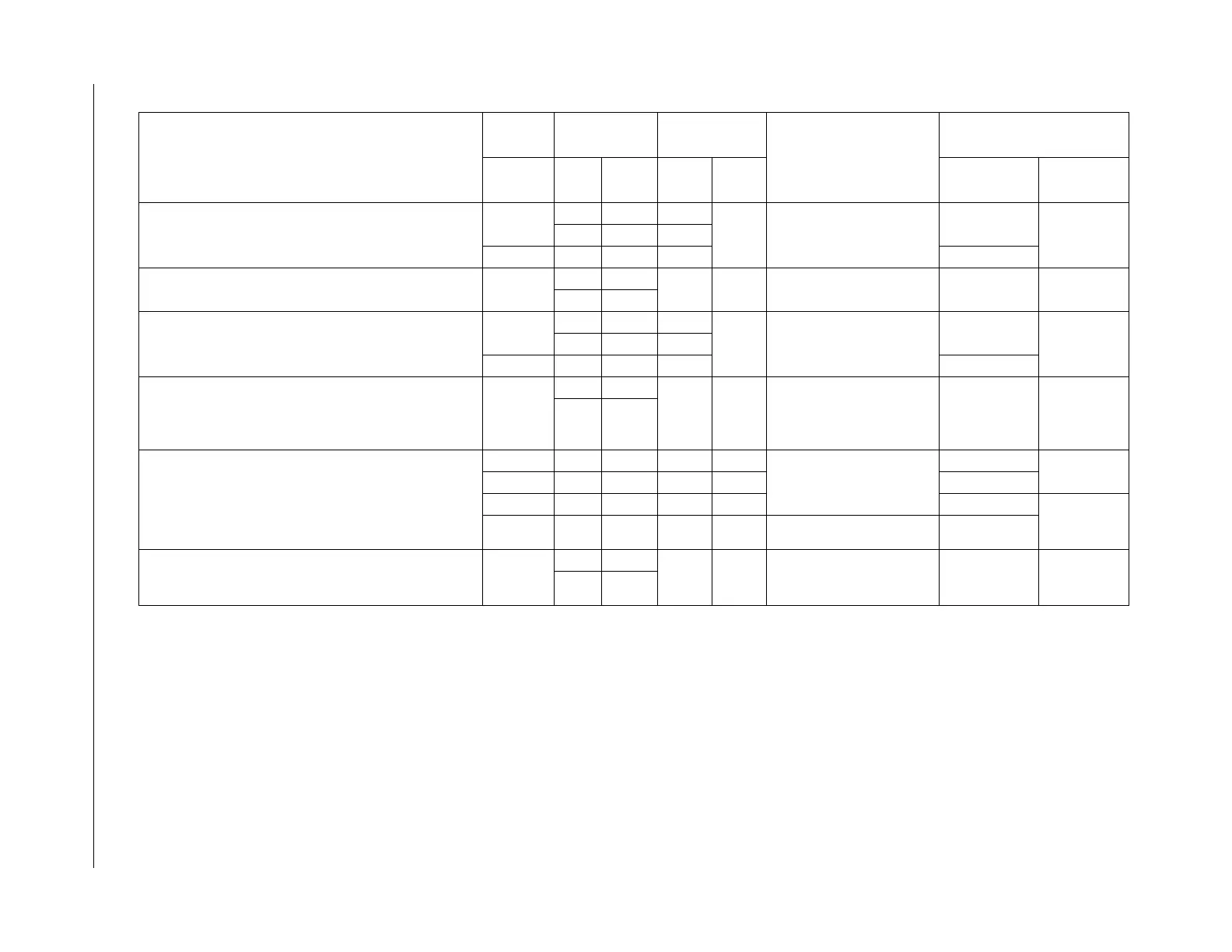

Table 3-2. Power Mode Selections

Mode of Operation

BDCSCR

BDM

SPMSC1

PMC

SPMSC2

PMC

CPU & Periph CLKs

Effects on Sub-System

ENBDM

1

1

ENBDM is located in the BDC status and control register (BDCSCR) which is write accessible only through BDC commands, see Chapter 17, “Development

Support.”

LVDE LVDSE LPR PPDC BDM Clock

Voltage

Regulator

RUN mode 0 x x 0 x on. ICS in any mode. off on

11 1

1xxx on

LPRUN mode 0 0 x 1 0 low freq required. ICS in

FBELP mode only.

off standby

10

WAIT mode - (Assumes WAIT instruction executed.) 0 x x 0 x CPU clock is off;

peripheral clocks on. ICS

state same as RUN mode.

off on

11 1

1xxx on

LPWAIT mode - (Assumes WAIT instruction executed.) 0 0 x 1 0 CPU clock is off;

peripheral clocks

at low speed. ICS in

FBELP mode.

off standby

10

STOP3 - (Assumes STOPE bit is set and STOP

instruction executed.) Note that STOP3 is used in

place of STOP2 if the BDM or LVD is enabled.

0 0 x x 0 ICS in STOP. LPO,

OSCOUT, ICSERCLK and

ICSIRCLK optionally on

2

2

Configured within the ICS module based on the settings of IREFSTEN, EFRESTEN, IRCLKEN, and ERCLKEN.

off standby

0 1 0 x 0 off

0 1 1 x x off on - stop

currents will

be increased

1 x x x x ICSLCLK still active. on

STOP2 - (Assumes STOPE bit is set and STOP

instruction executed.) If BDM or LVD is enabled,

STOP3 will be invoked rather than STOP2.

0 0 x 0 1 LPO and OSCOUT

optionally on

2,3

3

In stop2, CPU, flash, ICS and all peripheral modules are powered down except for the RTC.

off partial

powerdown

10

Loading...

Loading...