Chapter 3 Modes of Operation

MC9S08QE128 MCU Series Reference Manual, Rev. 2

Freescale Semiconductor 49

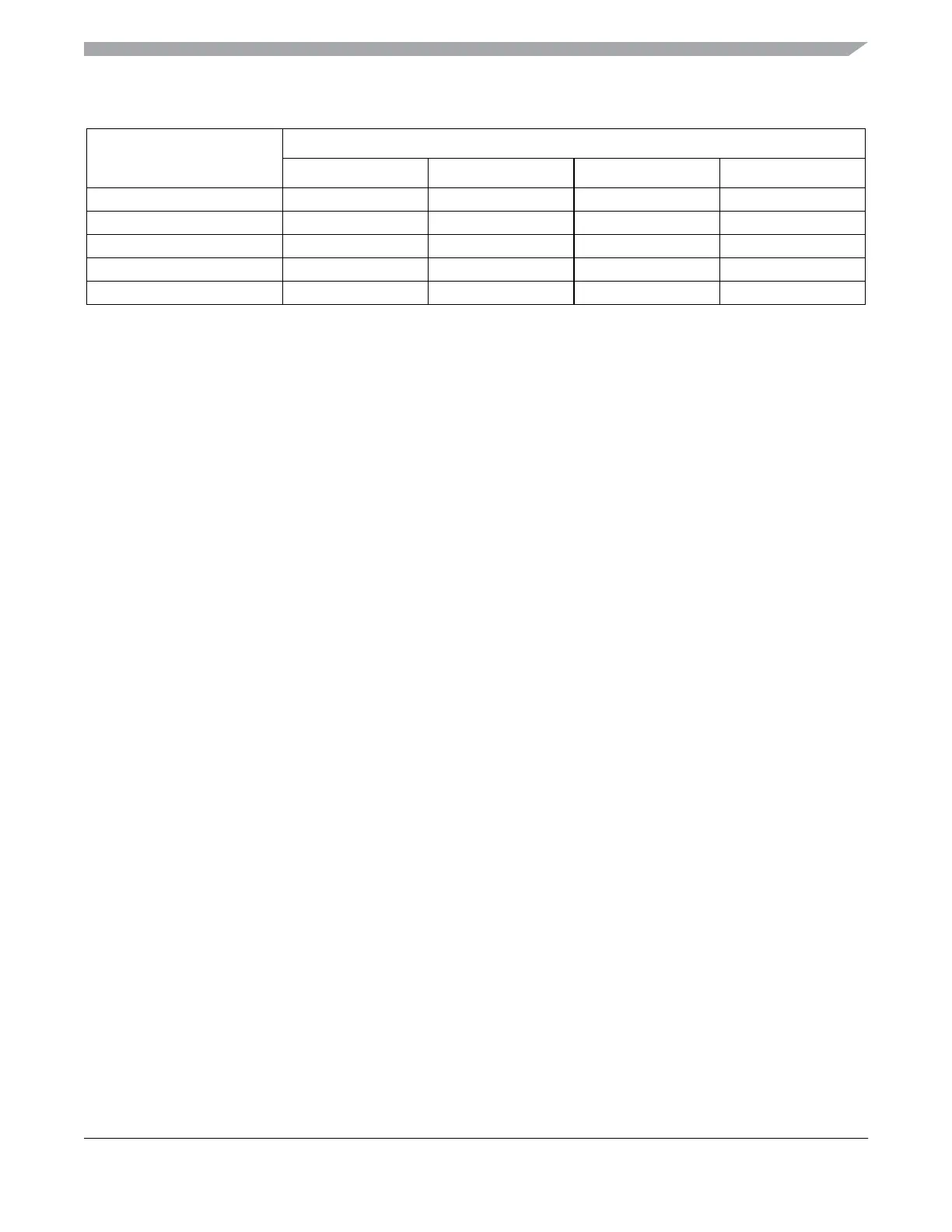

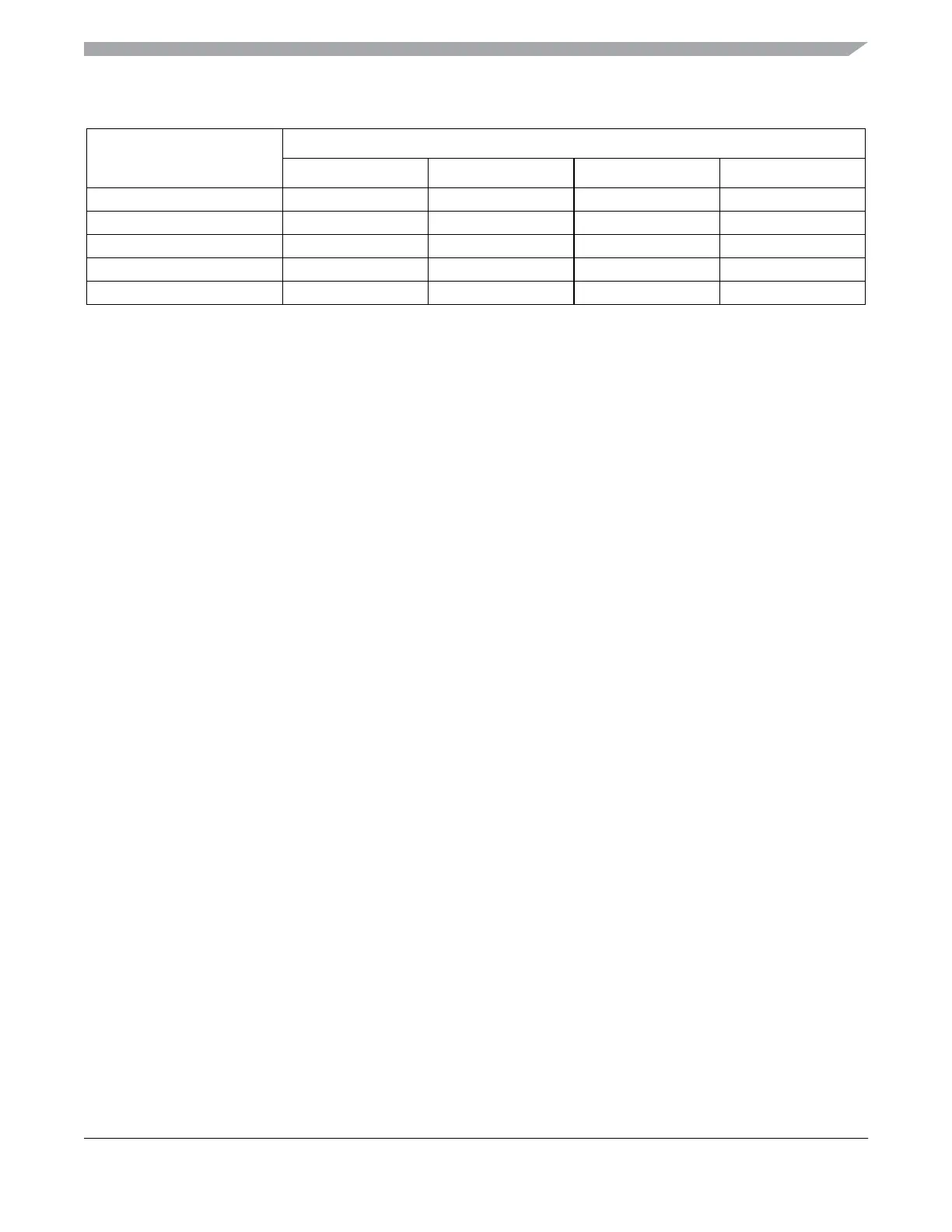

SCIx Off Standby Optionally On Optionally On

SPIx Off Standby Optionally On Optionally On

TPMx Off Standby Optionally On Optionally On

Voltage Regulator Partial Powerdown Optionally On

9

Standby Standby

XOSC Optionally On Optionally On

10

Optionally On Optionally On

1

Requires the asynchronous ADC clock. For stop3, LVD must be enabled to run in stop if converting the bandgap channel.

2

LVD must be enabled to run in stop if using the bandgap as a reference.

3

If ENBDM is set when entering stop2, the MCU will actually enter stop3.

4

If ENBDM is set when entering LPRun or LPWait, the MCU will actually stay in run mode or enter wait mode, respectively.

5

IRCLKEN and IREFSTEN set in ICSC1, else in standby.

6

ICS must be configured for FBELP, bus frequency limited to 125kHz in LPRUN or LPWAIT.

7

If LVDSE is set when entering stop2, the MCU will actually enter stop3.

8

If LVDSE is set when entering LPRun or LPWait, the MCU will actually enter run or wait mode, respectively.

9

Requires the LVD to be enabled, else in standby. See Section 3.6.4, “LVD Enabled in Stop Mode”.

10

ERCLKEN and EREFSTEN set in ICSC2, else in standby.

Table 3-4. Stop and Low Power Mode Behavior (continued)

Peripheral

Mode

Stop2 Stop3 LPWait LPRun

Loading...

Loading...