Date Code 20010518 SELOGIC Control Equations 7-9

SEL-2020 Instruction Manual

Processing Sequence

You may need to consider the order in which SEL

OGIC Control Equations are processed to fully

understand their operation and thereby ensure the desired result. When a SEL

OGIC Control

Equation contains, as one of its terms, the result of another SEL

OGIC Control Equation, the order

in which the equations are processed may affect the result. For example, consider three SEL

OGIC

Control Equations, A, B, and C, that are processed in alphabetic order. It takes 1 µs to process

each equation, and the group is processed every 15 ms. If SEL

OGIC Control Equation B contains

the results of equation A, the results of B will be current (within 1 µs) because A was processed

as part of the current process cycle. However, if equation B contains the results of equation C,

the results of B will not be current because the results of C are from the previous process cycle,

which is now 15 ms old.

The SEL-2020 processes SEL

OGIC Control Equation in the following order and frequency (see

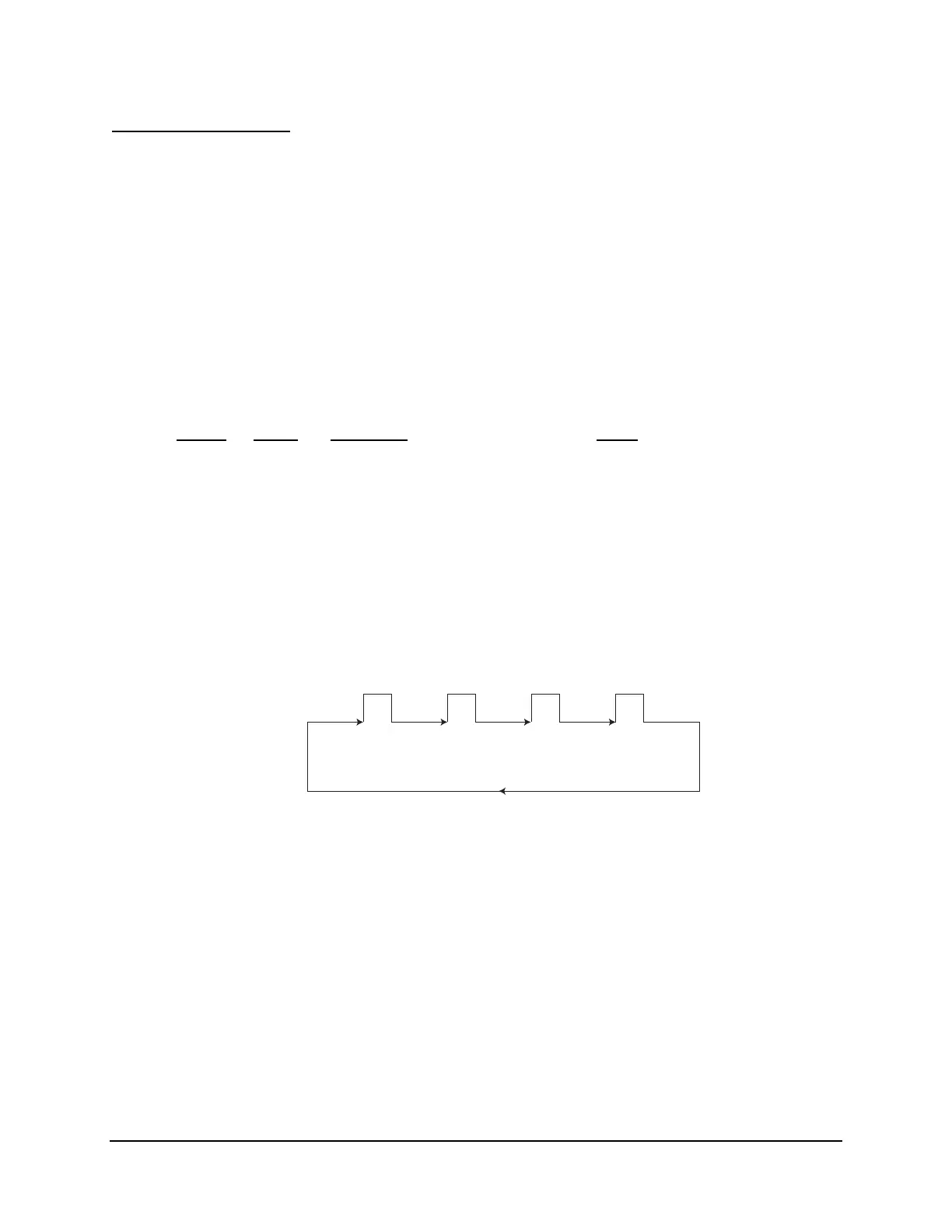

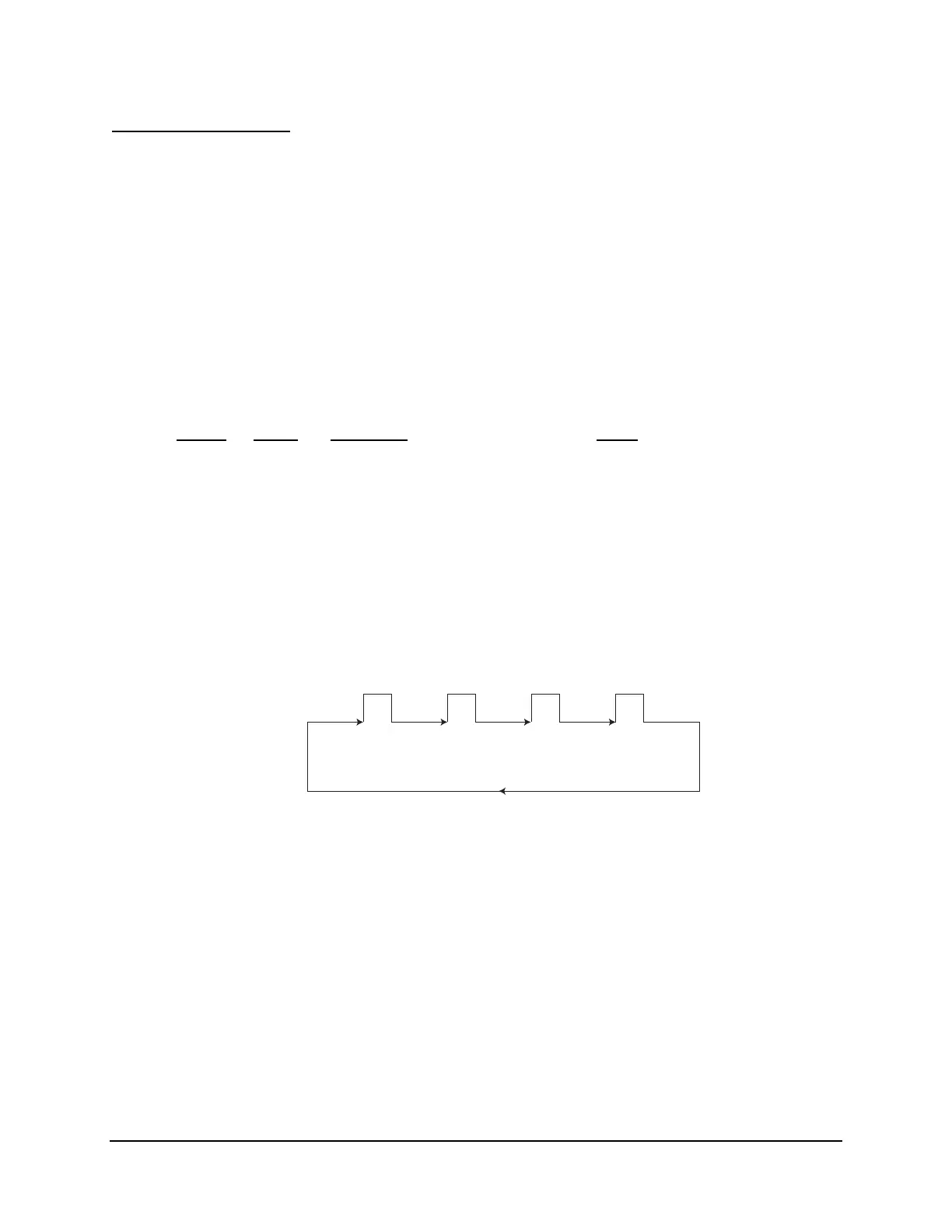

Figure 7.8 for an illustration of this processing sequence):

Symbol Period Description Order

0 3.9 ms Output SEL

OGIC Control Equations OUT1 to OUT4

I 15.6 ms Intermediate Logic V,W,X,XT,Y,YT,Z,ZT

1-16 15.6 ms Port Logic (e.g. 3 = Port 3 Logic) SBR1, SBR2, …, SBR16,

CBR1, CBR2, …, CBR16

SRB1, SRB2, …, SRB16,

CRB1, CRB2, …, CRB16,

ISSUE1 to ISSUE12,

ISSUE1A to ISSUE3A,

BR1, BR2, …, BR16,

RB1, RB2, …, RB16

0,I,1,5,9,13 0,2,6,10,14 0,3,7,11,15 0,4,8,12,16

Figure 7.8: Processing Sequence Illustration

To illustrate the effects of the processing sequence, consider the following equations:

W=V Equation 1

V=W Equation 2

ISSUE1=1:UMB*!D1 Equation 3

In Equation 1, V is processed before W, so W will always exactly match V in value. However,

in Equation 2, V will always lag W by 15.6 milliseconds because V is processed before W; V is

being assigned the value W was set to during the last processing interval. In Equation 3, the

issue condition will be true for one processing interval, because D1 is found based on the

ISSUE1 value; so the D1 used in the equation will be the result of the previous processing

interval's computations.

Loading...

Loading...