table 190 contains a list of the fault conditions that lead to a fault indication.

Table 190: SPI errors

Fault condition of the SPI Fault indication

Incorrect number of CLK impulses spi_miso at high level

Write command without data spi_miso at high level

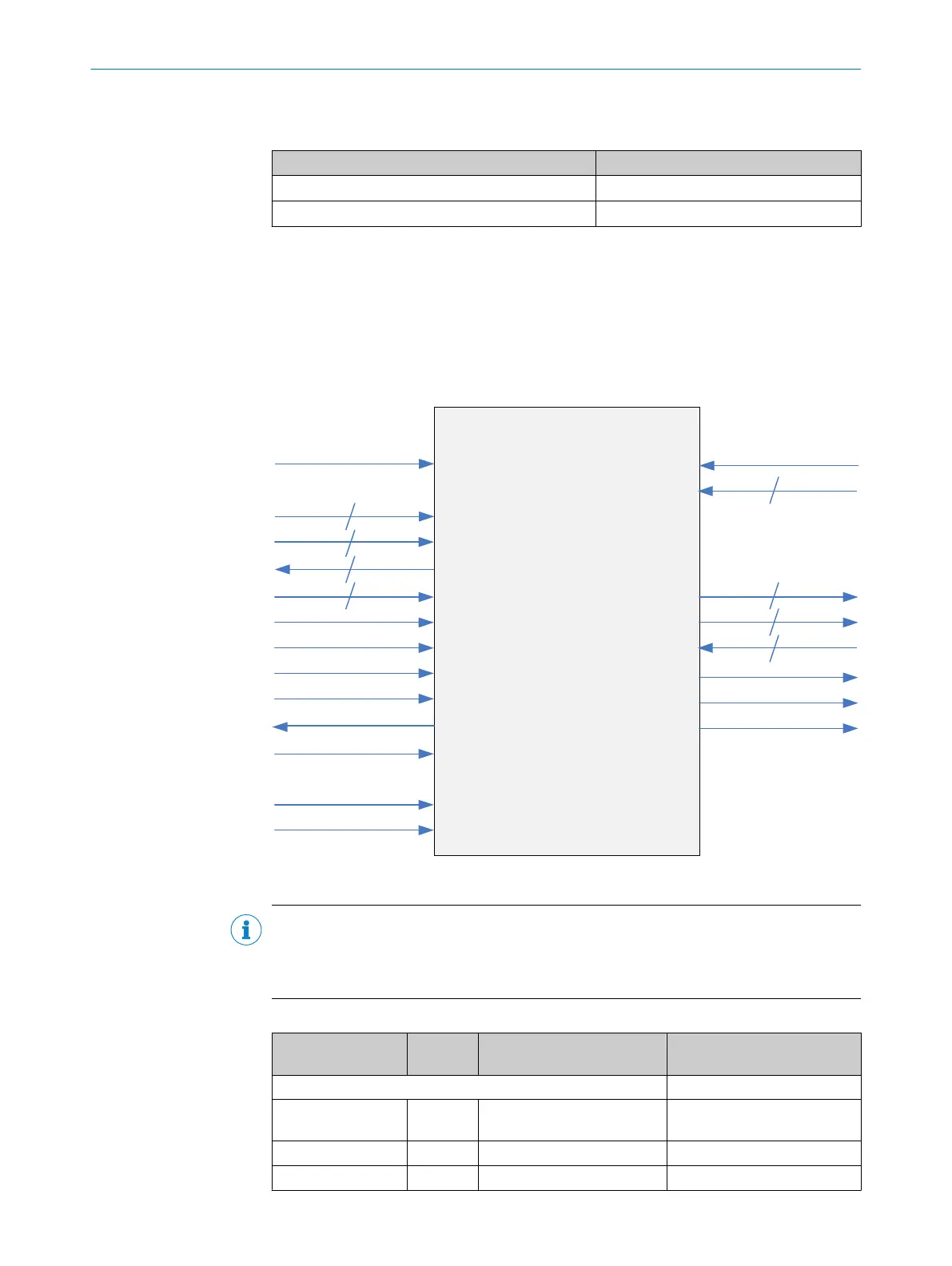

9.3 Parallel interface block

As an example, a parallel interface block is supplied together with the IP Core.

The parallel interface block follows the Texas Instruments Asynchronous External Mem‐

ory Interface A (EMIFA). The reference document for this interface is the User's Guide

SPRUFL6E, dated April 2010.

The figure and table below show the interface signals.

Parallel Interface (EMIFA)

clk rst

dsl_a(0:5)

dsl_di(0:15)

dsl_do(0:15)

dsl_ce_l

bit_period(0:2)

hostd_a(0:6)

hostd_di(0:7)

hostd_do(0:7)

hostd_r

hostd_w

hostd_f

User interface IP-Core interface

dsl_oe_l

dsl_we_l

dsl_wait

dsl_freeze

dsl_8n16

bigend

dsl_ba

dsl_be(0:1)

Figure 38: Parallel interface block signals

NOTE

Please note that the EMIFA block supplied with the HIPERFACE DSL

®

IPCore is only fit

for the usage with drive interface. It can be adapted to safe 1 and safe 2 interfaces if

needed, but it is not suggested.

Table 191: Parallel interface block signals

Pin name Model

name

Function Note

Host interface

ema_clk Input Clock input Separate clock domain to the

IP Core

dsl_a(5:0) Input EMIFA: Address bus

dsl_di(15:0) Input EMIFA: Data bus input

FPGA IP-CORE 9

8017595/ZTW6/2018-01-15 | SICK T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

145

Subject to change without notice

Loading...

Loading...