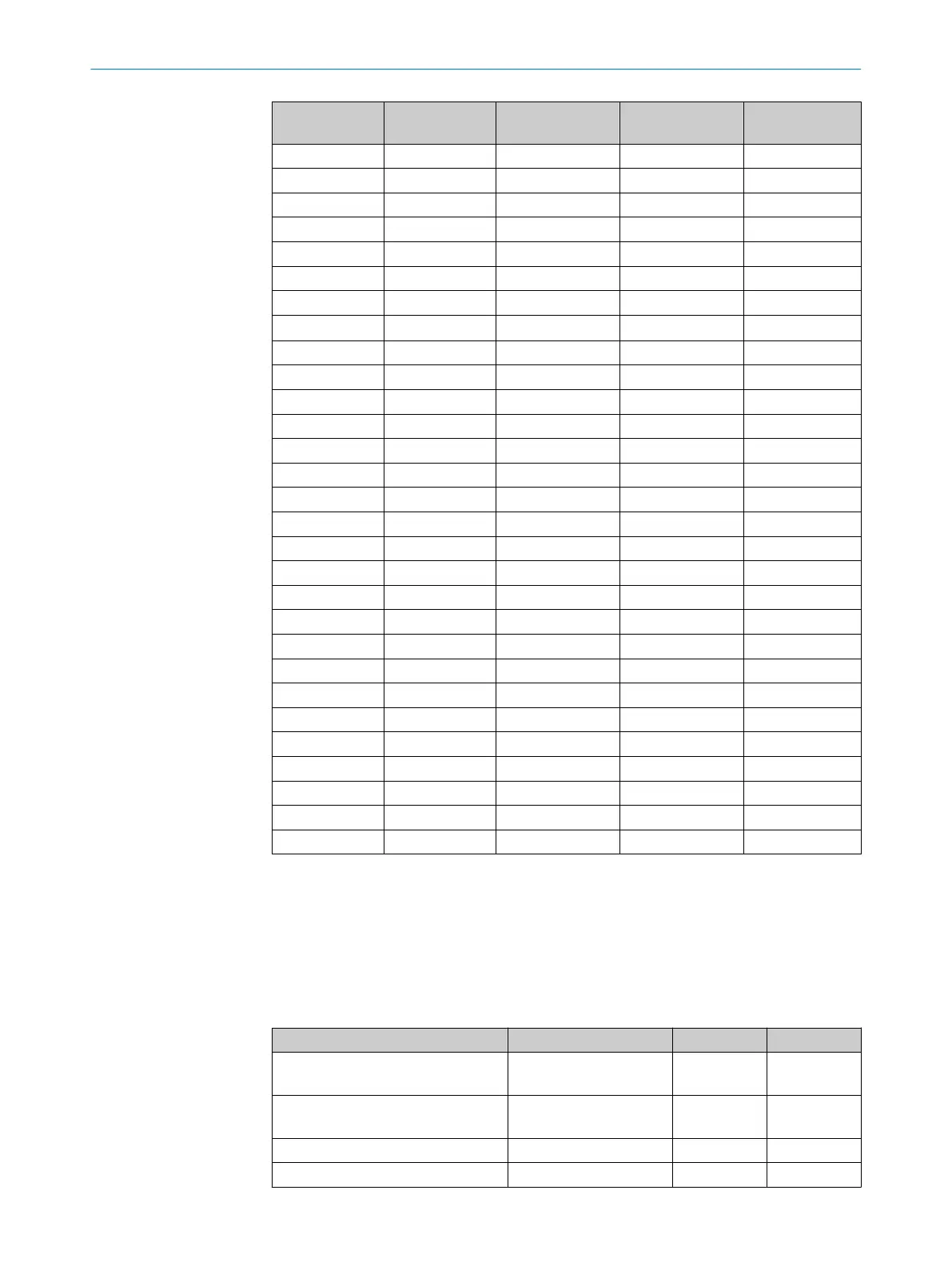

Designation 8 bit, Big-Endian 8 bit, Little-Endian 16 bit, Big-Endian 16 bit, Little-

Endian

SUMMARY 18h 1Eh 18h (15:8) 1Eh ( 7:0)

VPOS4 19h 1Fh 18h ( 7:0) 1Eh (15:8)

VPOS3 1Ah 1Bh 1Ah (15:8) 1Ah (15:8)

VPOS2 1Bh 1Ah 1Ah ( 7:0) 1Ah ( 7:0)

VPOS1 1Ch 19h 1Ch (15:8) 18h (15:8)

VPOS0 1Dh 18h 1Ch ( 7:0) 18h ( 7:0)

VPOSCRC_H 1Eh 1Dh 1Eh (15:8) 1Ch (15:8)

VPOSCRC_L

1Fh 1Ch 1Eh ( 7:0) 1Ch ( 7:0)

PC_BUFFER0 20h 20h 20h (15:8) 20h ( 7:0)

PC_BUFFER1 21h 21h 20h ( 7:0) 20h (15:8)

PC_BUFFER2 22h 22h 22h (15:8) 22h ( 7:0)

PC_BUFFER3 23h 23h 22h ( 7:0) 22h (15:8)

PC_BUFFER4 24h 24h 24h (15:8) 24h ( 7:0)

PC_BUFFER5 25h 25h 24h ( 7:0) 24h (15:8)

PC_BUFFER6 26h 26h 26h (15:8) 26h ( 7:0)

PC_BUFFER7 27h 27h 26h ( 7:0) 26h (15:8)

PC_ADD_H 28h 2Bh 28h (15:8) 2Ah (15:8)

PC_ADD_L 29h 2Ah 28h ( 7:0) 2Ah ( 7:0)

PC_OFF_H 2Ah 29h 2Ah (15:8) 28h (15:8)

PC_OFF_L 2Bh 28h 2Ah ( 7:0) 28h ( 7:0)

PC_CTRL 2Ch 2Dh 2Ch (15:8) 2Ch (15:8)

PIPE_S 2Dh 2Fh 2Ch ( 7:0) 2Eh (15:8)

PIPE_D 2Eh 2Eh 2Eh (15:8) 2Eh ( 7:0)

PC_DATA 2Fh 2Ch 2Eh ( 7:0) 2Ch ( 7:0)

ACC_ERR_CNT 38h 38h 38h (15:8) 38h ( 7:0)

MAXACC 39h 39h 38h ( 7:0) 38h (15:8)

MAXDEV_H 3Ah 3Bh 3Ah (15:8) 3Ah (15:8)

MAXDEV_L 3Bh 3Ah 3Ah ( 7:0) 3Ah ( 7:0)

DUMMY 3Fh 3Fh n/v n/v

9.6 Implementation of the IP Core for Xilinx Spartan-3E/6

The DSL Master IP Core is provided by SICK for Xilinx Spartan-3E and Spartan-6 FPGA

components.

table 196 lists the requirements that must be fulfilled for the FPGA components

selected.

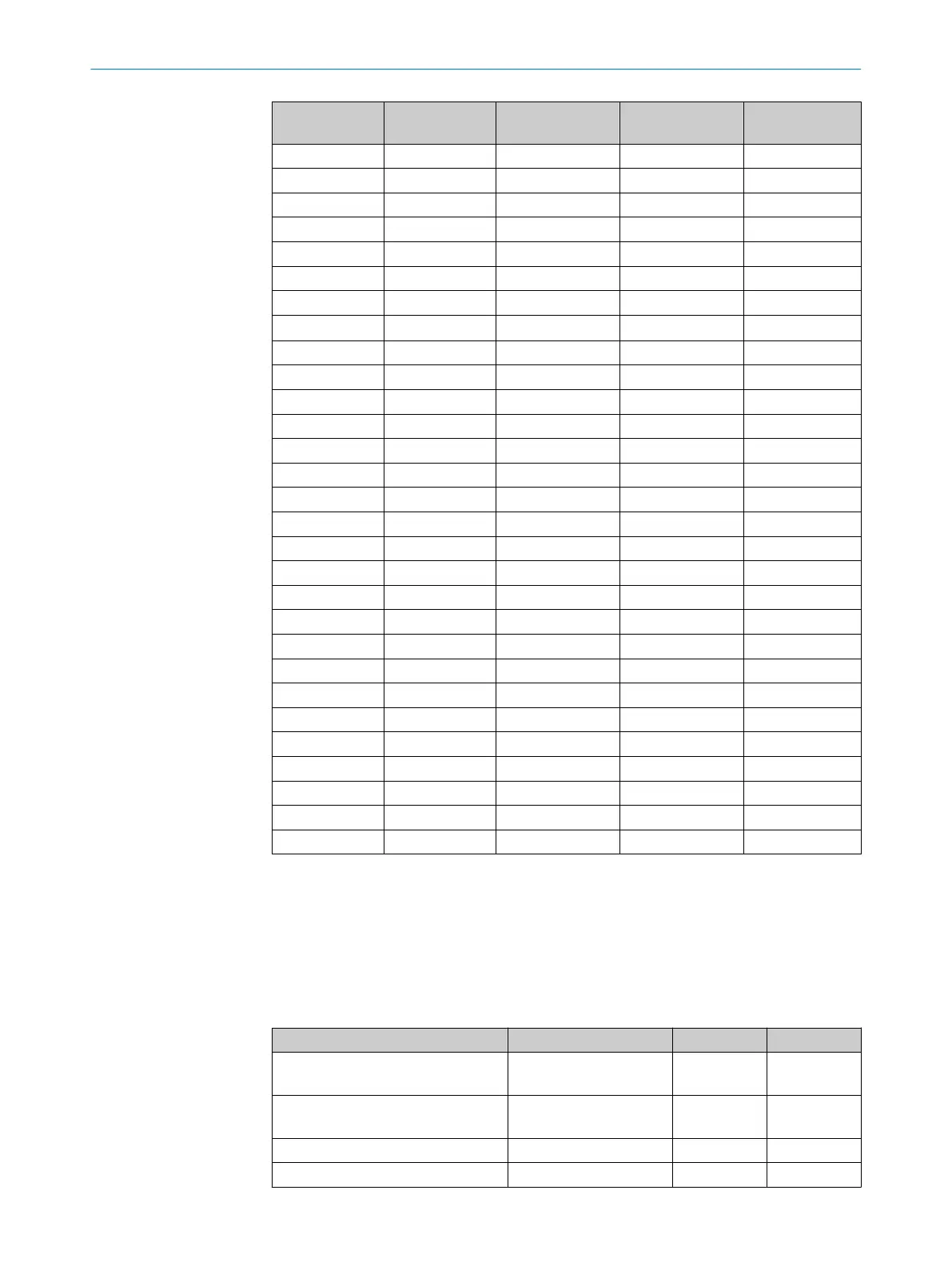

Table 198: Requirements of Xilinx Spartan-3E/6 FPGAs

FPGA requirements IP Core variant Spartan-3E Spartan-6

Supported "Speed Grades" -4

-5

-3

-2

Number of "Slices" used / "Slice reg‐

ister"

Standard, serial 2,522 1,882

Number of "BUFG/BUFGMUX" used 1 1

Timing requirements (clk periods) 13 ns 13 ns

FPGA IP-CORE 9

8017595/ZTW6/2018-01-15 | SICK T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

151

Subject to change without notice

Loading...

Loading...