6.3.26 Fast position estimator deviation

The MAXDEV registers return the maximum absolute position deviation while the posi‐

tion estimator is active. The returned 16 bit value has the same format (resolution) as

the fast position channel and is clamped to a maximum of 65535 steps (0xFFFF). The

registers are set to the maximum value 0xFFFF at reset.

These registers also allow setting a deviation threshold value for triggering the output

signal dev_thr_err (see chapter 5.4.3). The threshold value can be written with the

same format as the deviation (unsigned 16 bit, same resolution as the fast position

channel).

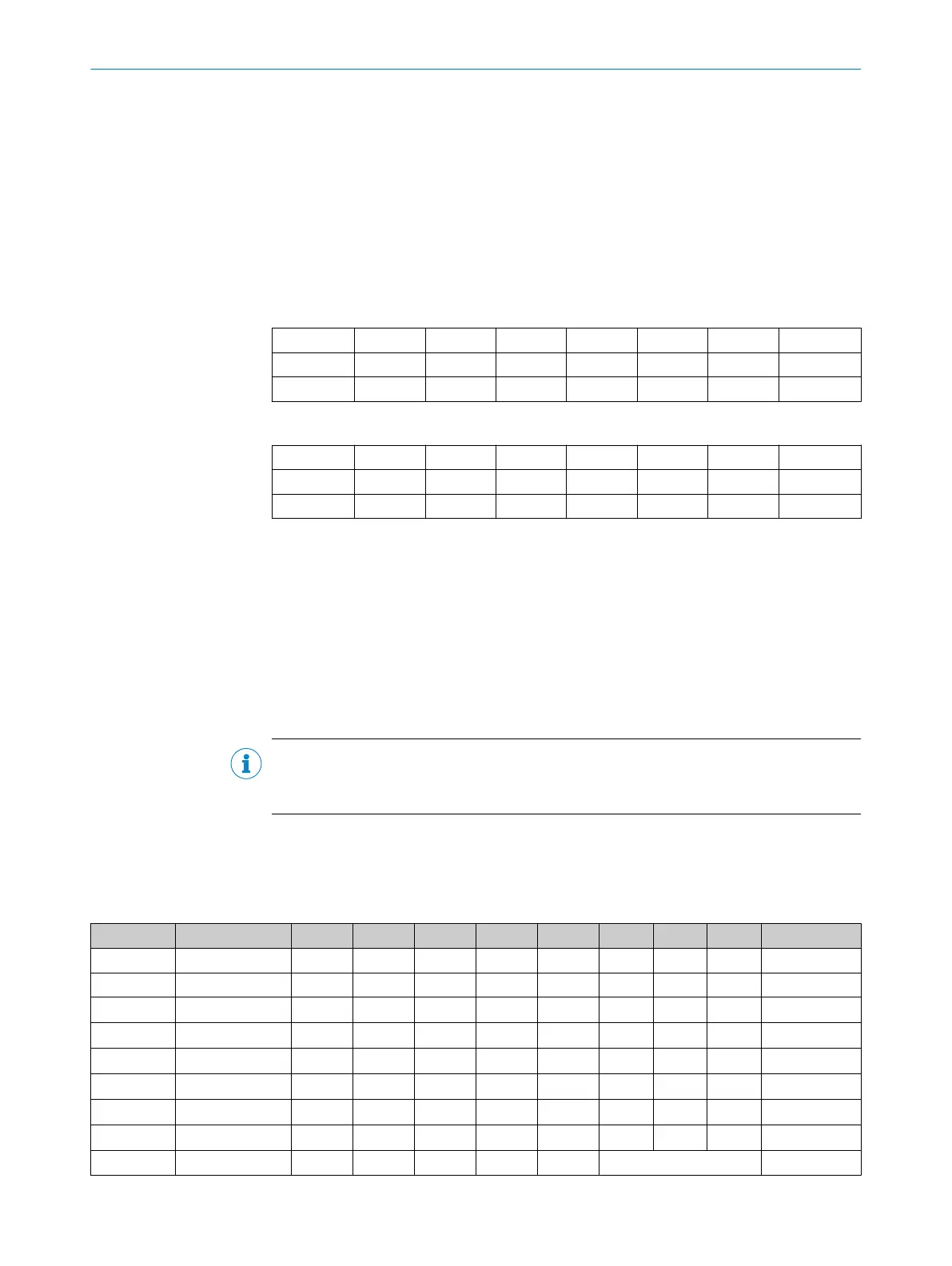

Register 3Ah: Fast position estimator deviation high byte

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

DEV15 DEV14 DEV13 DEV12 DEV11 DEV10 DEV09 DEV08

Bit 15 Bit 8

Register 3Bh: Fast position estimator deviation low byte

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

DEV07 DEV06 DEV05 DEV04 DEV03 DEV02 DEV01 DEV00

Bit 7 Bit 0

Bit 15-0

DEV15:DEV00: Position deviation/Deviation threshold

Read: 16 bit value of position deviation

Write: 16 bit value for deviation threshold for dev_thr_err

6.4

Function register for the DSL Slave

The remote registers of the DSL Slave (encoder) are mirrored in the DSL Master under

the addresses 40h to 7Fh. These registers are accessible using "short message" trans‐

actions (see chapter 7.5.1).

NOTE

It should be noted that the DSL Slave register can only be accessed via 8 bit address‐

ing. The bigend option does not affect the Slave register address allocation.

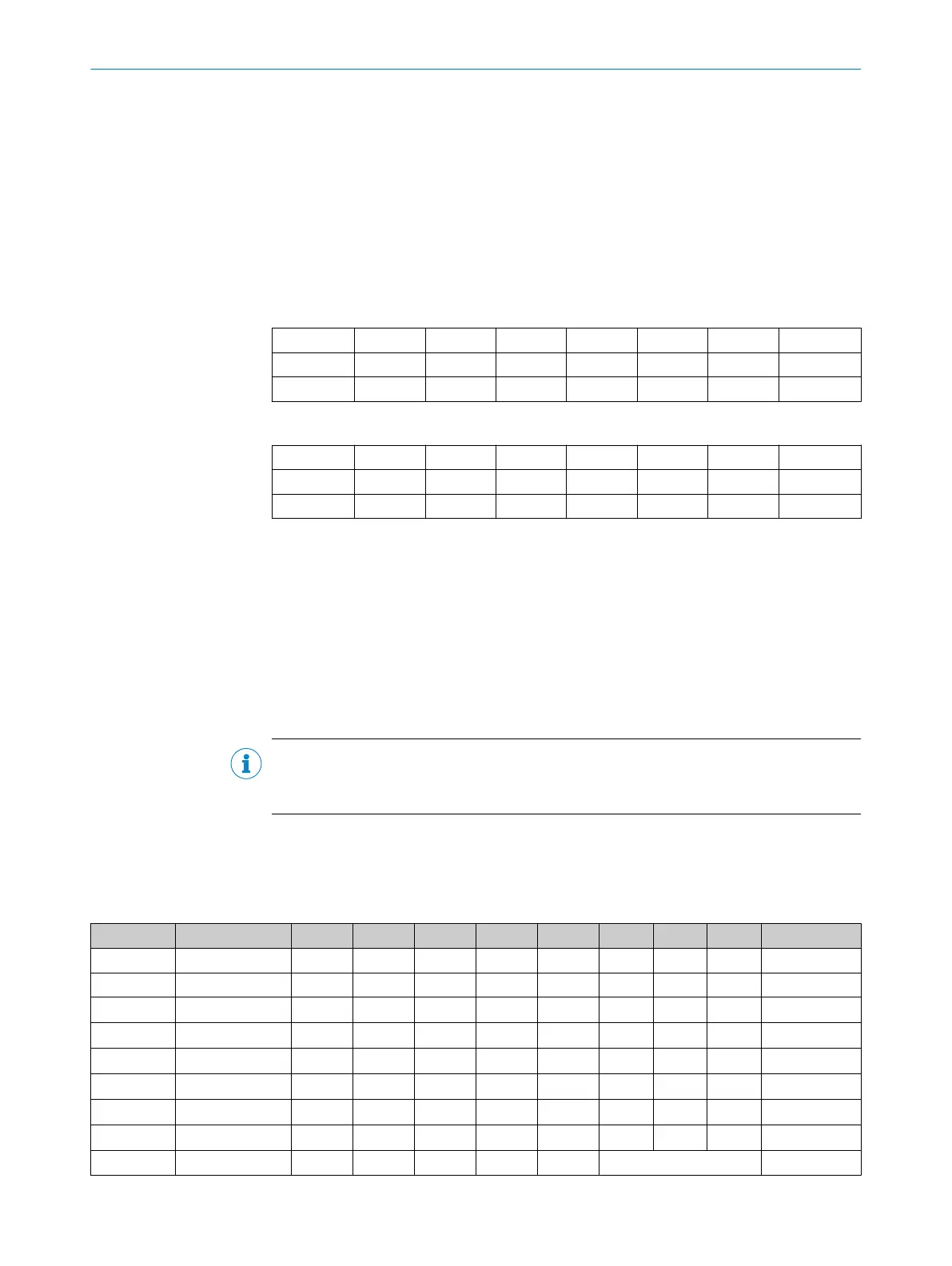

The minimum number of remote registers present in the DSL Slave is set out in

table 26. For real DSL Slave installations, more remote registers can be installed than

are set out in the table.

Table 26: Remote slave register

Address Designation Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value at reset

40h ENC_ST0 ST07 ST06 ST05 ST04 ST03 ST02 ST01 ST00 0000 0000

41h ENC_ST1 ST17 ST16 ST15 ST14 ST13 ST12 ST11 ST10 0000 0000

42h ENC_ST2 ST27 ST26 ST25 ST24 ST23 ST22 ST21 ST20 0000 0000

43h ENC_ST3 ST37 ST36 ST35 ST34 ST33 ST32 ST31 ST30 0000 0000

44h ENC_ST4 ST47 ST46 ST45 ST44 ST43 ST42 ST41 ST40 0000 0000

45h ENC_ST5 ST57 ST56 ST55 ST54 ST53 ST52 ST51 ST50 0000 0000

46h ENC_ST6 ST67 ST66 ST65 ST64 ST63 ST62 ST61 ST60 0000 0000

47h ENC_ST7 ST77 ST76 ST75 ST74 ST73 ST72 ST71 ST70 0000 0000

7Ch SRSSI - - - - - SRSSI2:0 ---- -000

REGISTER MAP 6

8017595/ZTW6/2018-01-15 | SICK T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

55

Subject to change without notice

Loading...

Loading...