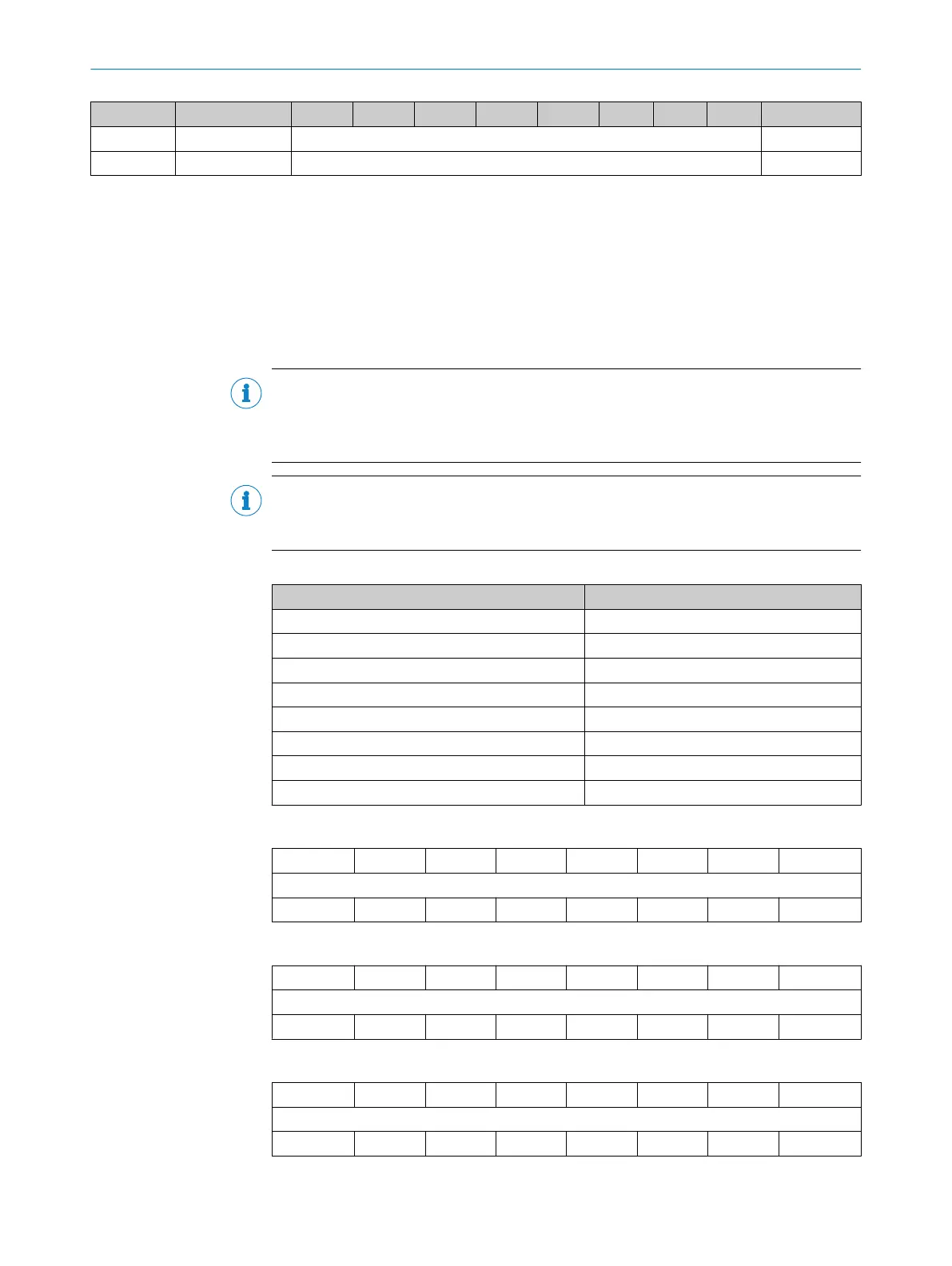

Address Designation Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Value at reset

7Eh MAIL Slave-Mail 0000 0000

7Fh PING Slave-Ping

1

0000 0000

1

After a protocol reset, the PING register contains the slave interface version (see chapter 6.4).

6.4.1 Encoder status

The ENC_ST encoder status registers contain all slave system errors, events and warn‐

ings from the DSL encoder.

The allocation between the individual bits and the slave system statuses is determined

when the DSL Slave is installed and set out in the associated data sheet. The general

application of the status register follows the list in chapter 7.6.3.

NOTE

It should be noted that all bits of an encoder status register are OR linked and mirror

bits in the SAFE_SUM DSL Master register (36h) (see figure 14). In this way the appro‐

priate groups can react rapidly to slave statuses.

NOTE

Bits in the encoder status register can only be set by the DSL Slave and only deleted by

the frequency inverter application (acknowledgment).

Table 27: Encoder status and summary register

Encoder status SAFE_SUM bit (DSL Master 36h)

ENC_ST0 (40h) SUM0

ENC_ST1 (41h) SUM1

ENC_ST2 (42h) SUM2

ENC_ST3 (43h) SUM3

ENC_ST4 (44h) SUM4

ENC_ST5 (45h) SUM5

ENC_ST6 (46h) SUM6

ENC_ST7 (47h) SUM7

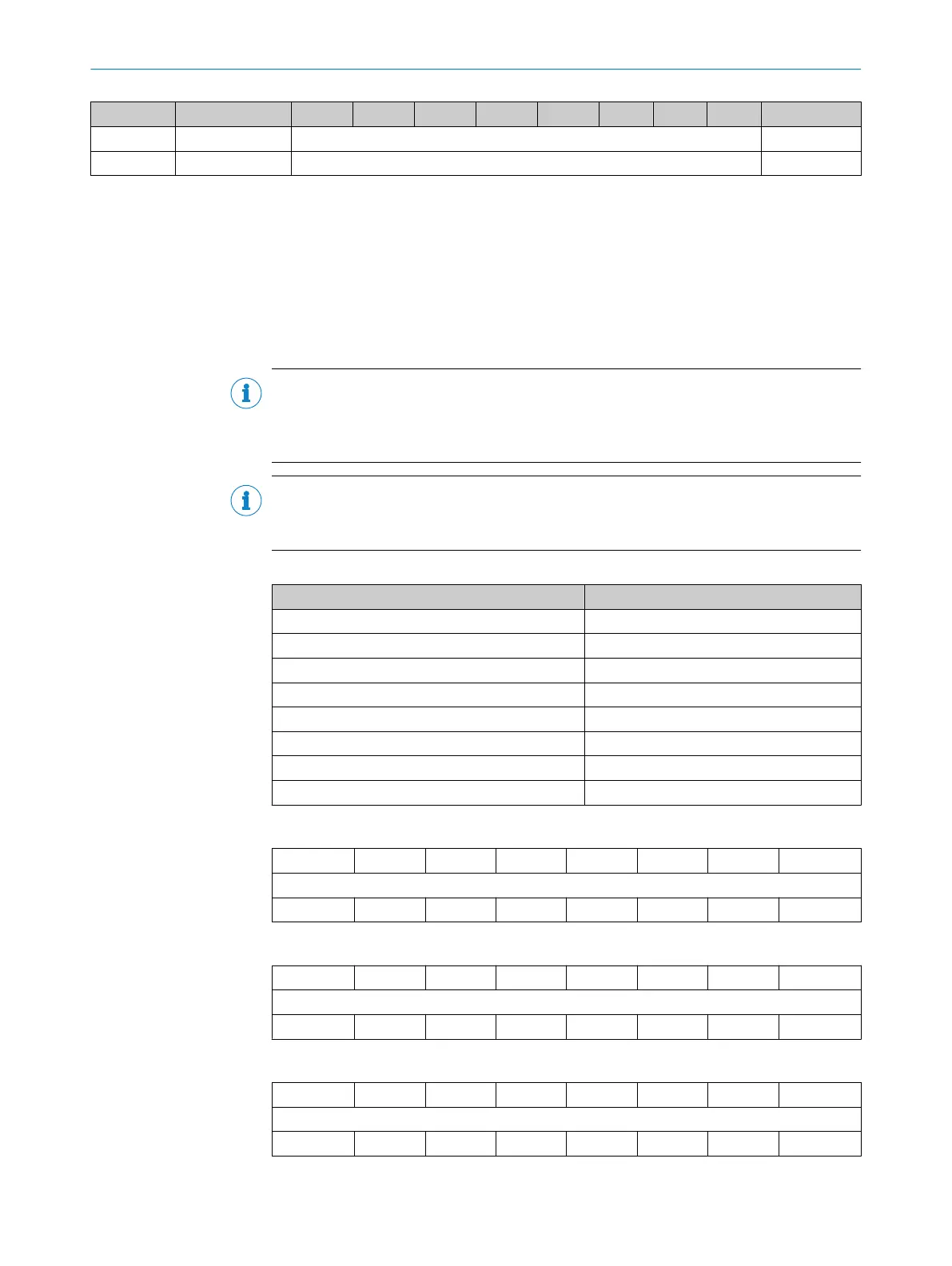

Register 40h: Encoder status, byte 0

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 7 Bit 0

Register 41h: Encoder status, byte 1

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 15 Bit 8

Register 42h:

Encoder status, byte 2

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 23 Bit 16

Register 43h:

Encoder status, byte 3

6

REGISTER MAP

56

T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

8017595/ZTW6/2018-01-15 | SICK

Subject to change without notice

Loading...

Loading...