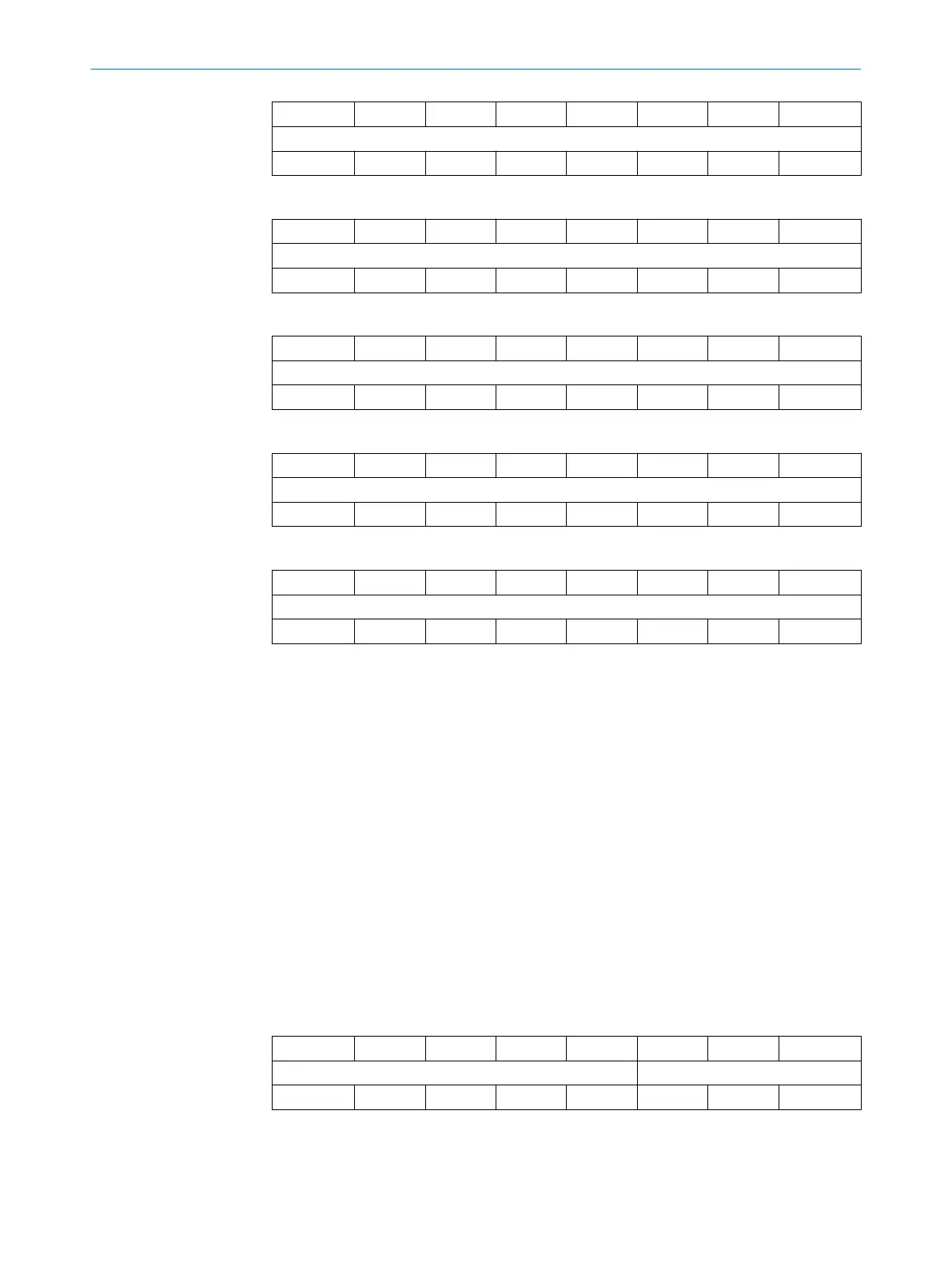

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 31 Bit 24

Register 44h: Encoder status, byte 4

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 39 Bit 32

Register 45h: Encoder status, byte 5

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 47 Bit 40

Register 46h: Encoder status, byte 6

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 55 Bit 48

Register 47h:

Encoder status, byte 7

R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0 R/C-0

Encoder status

Bit 63 Bit 56

Bit 63-0

Encoder status

The individual bits indicate different errors, events and warnings. The meaning of each

individual bit is determined by the particular DSL Slave installation. Generally the speci‐

fication in chapter 7.6.3 applies.

1 = Error, event or warning status.

0 = Encoder in normal status.

6.4.2 Slave RSSI

The SRSSI register for indicating the received signal strength at the slave (Slave

Received Signal Strength Indicator, RSSI) provides an indication of the strength of the

signal arriving at the slave.

The value of the register is only updated from frame to frame if the measurement result

deteriorates. After a read access to this register, the register is reset to the value "7"

(maximum signal strength).

The register is write protected.

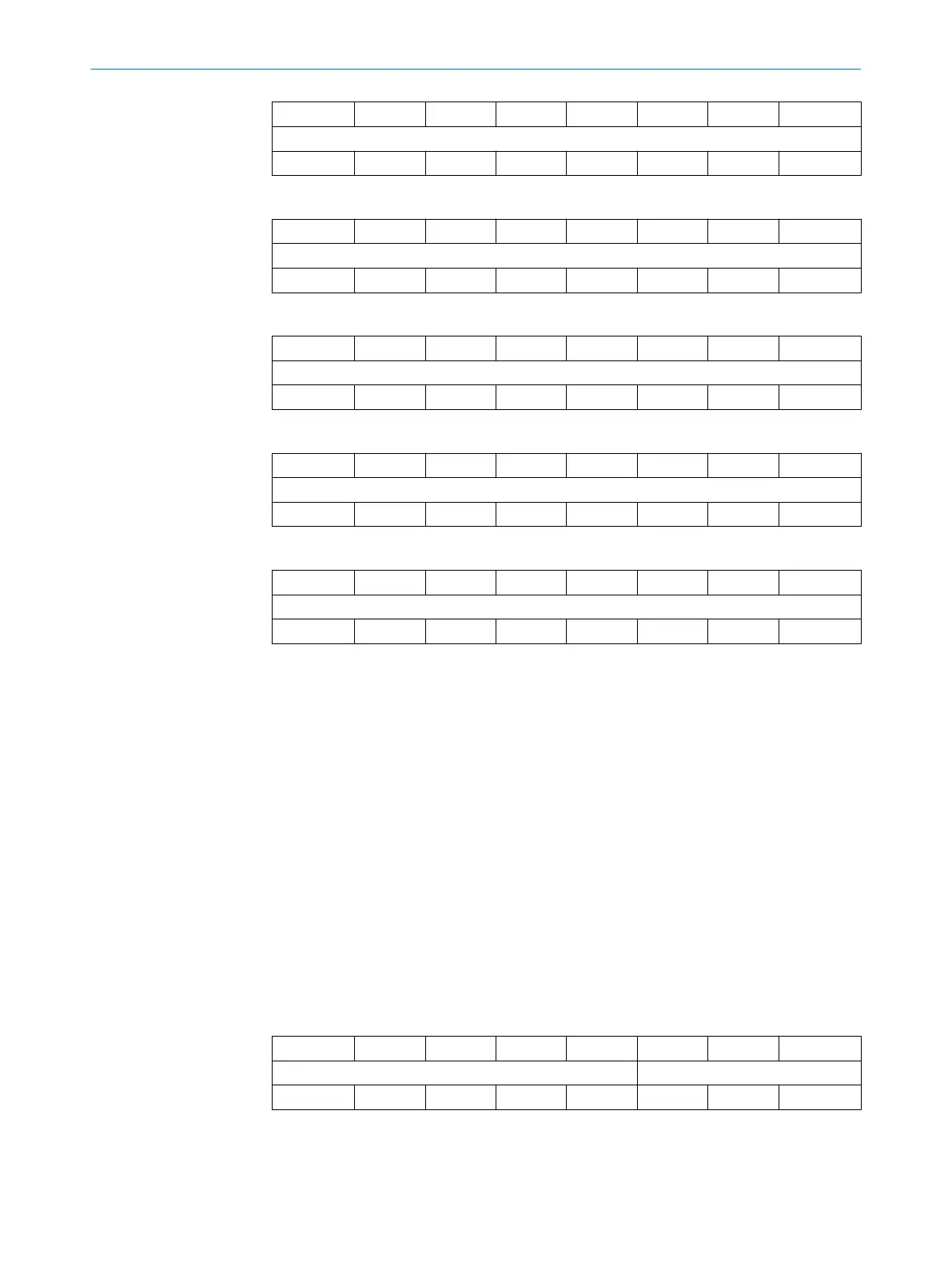

Register 7Ch:

Slave RSSI

X-0 X-0 X-0 X-0 X-0 R-0 R-0 R-0

SRSSI

Bit 7 Bit 0

Bit 7-3 Not implemented: Read as "0".

Bit 2-0 Value of the Slave RSSI

REGISTER MAP 6

8017595/ZTW6/2018-01-15 | SICK T E C H N I C A L I N F O R M A T I O N | HIPERFACE DSL

®

57

Subject to change without notice

Loading...

Loading...