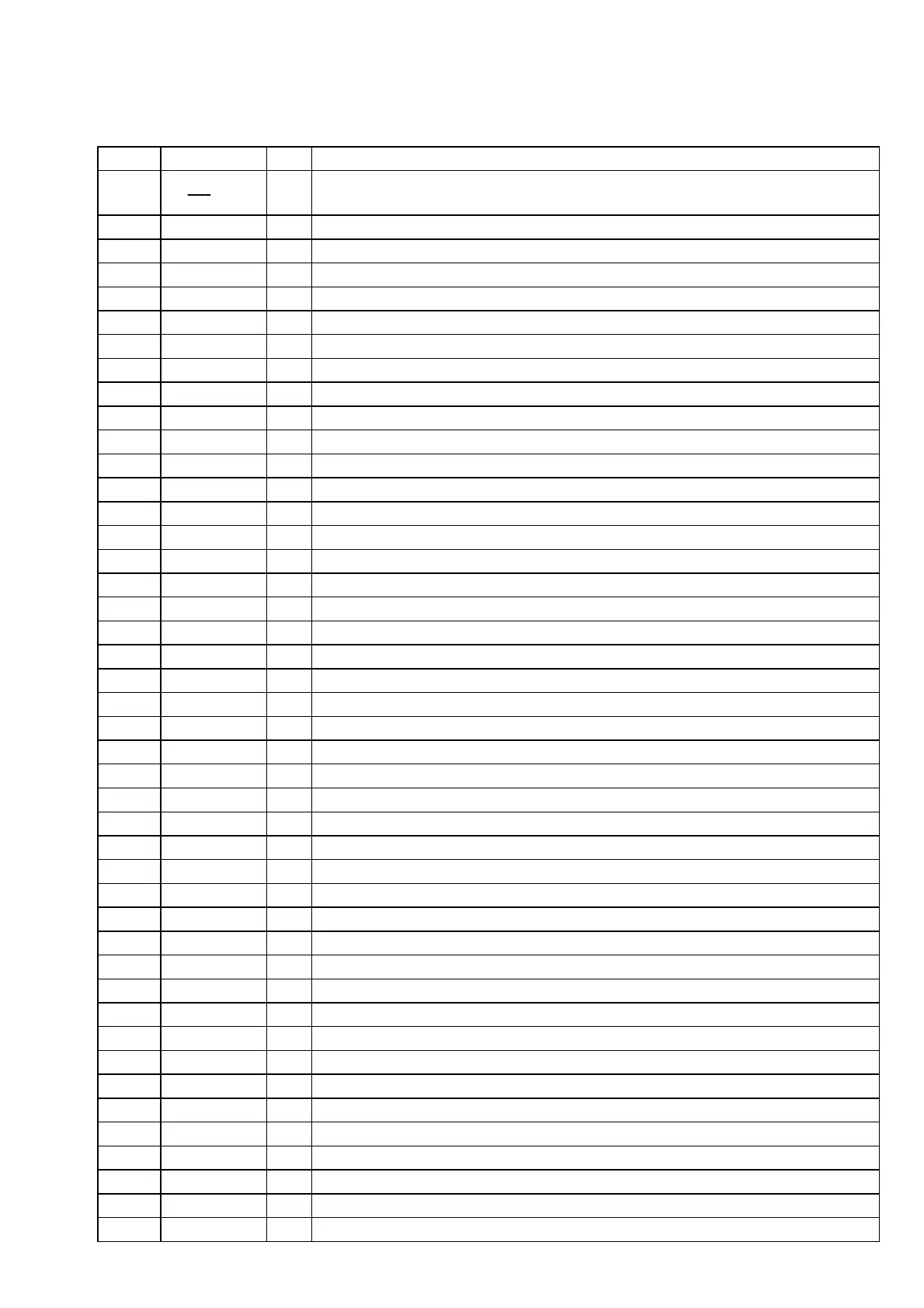

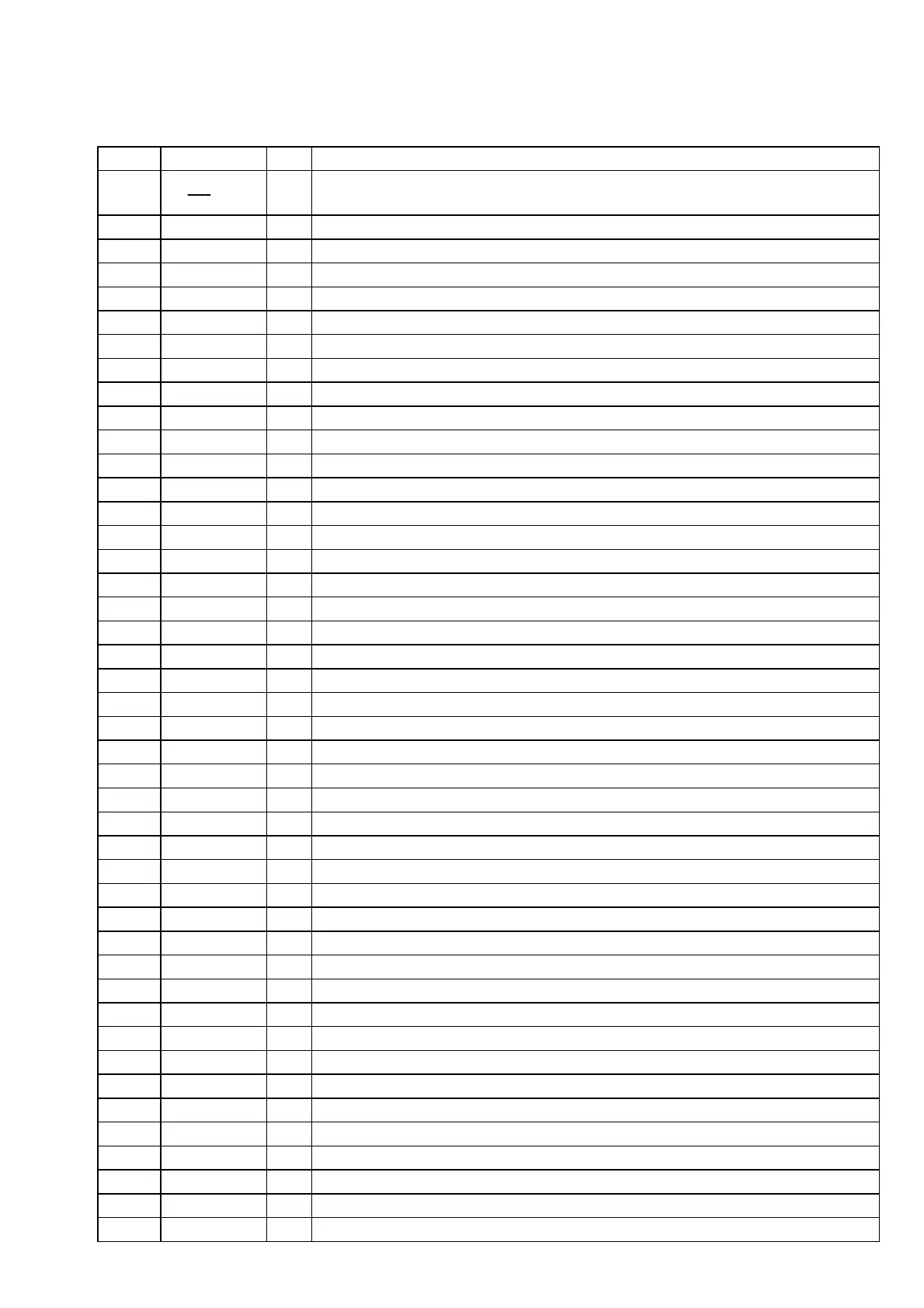

47

HCD-DX80

• MAIN BOARD IC501 M30620MCA-A95FP (SYSTEM CONTROLLER)

Pin No. Pin Name I/O Description

1

AUDIO OUT

ON/OFF

O

Audio output signal on/off control “H”: ON, “L”: OFF Not used (open)

2

STEREO I Stereo detection signal input from the LA1845 (IC11) “L”: Stereo in

3

TUNED

I

Tuning detection signal input from the LA1845 (IC11) “L”: Tuned in

4

SIRCS

I

Remote commander receiver signal input terminal

5 SUR1 O

Surround control signal output terminal not used (open)

6 SUR2 O

Surround control signal output terminal not used (open)

7

SUR3

O

Surround control signal output terminal not used (open)

8

GND — Ground terminal

9 GND

— Ground terminal

10

XC IN I Sub system clock input terminal (32.768 kHz)

11

XC OUT O Sub system clock output terminal (32.768 kHz)

12

RESET I System reset signal input from the reset signal generator (IC502) “L”: reset

13 X-OUT

O Main system clock output terminal (16 MHz)

14 VSS

— Ground terminal

15 X-IN

I Main system clock input terminal (16 MHz)

16 VCC

— Power supply terminal (+5V)

17

NMI I For pull up terminal (connected to Ever +5V)

18 RDS-INT

I RDS interrupt signal input terminal Not used (connected to ground)

19 SCOR

I Subcode sync (S0+S1) detection signal input from the CXD3017Q (IC101)

20 RDS-DATA I

RDS data signal input terminal Not used (connected to ground)

21 ST-MUTE O

Muting on/off control signal output to the LA1845 (IC11)

22 ST-CE O

PLL chip enable signal output to the FM/AM PLL (IC51)

23 ST-DOUT

O PLL serial data output to the FM/AM PLL (IC51)

24 BU-PWM3

O RF data control signal output to the CXA2581N (IC103)

25

ST-DIN I PLL serial data input from the FM/AM PLL (IC51)

26 BU-PWM2

O Tracking error control signal output to the CXA2581N (IC103)

27

ST-CLK

O

PLL serial data transfer clock signal output to the FM/AM PLL (IC51)

28

BU-PWM1 O Focus error control signal output to the CXA2581N (IC103)

29

IIC-CLK I/O Shift clock signal input/output for the IIC bus

30

IIC-DATA I/O Data input/output terminal for the IIC bus

31

TXD1 O Not used (open)

32

SQ-DATA I Subcode Q data input from the CXD3017Q (IC101)

33

SQ-CLK O Subcode Q data reading clock signal output to the CXD3017Q (IC101)

34

SENS I Internal status detection monitor input from the CXD3017Q (IC101)

35

CD-DATA O Serial data output to the CXD3017Q (IC101)

36

NC — Not used (fixed at “L”)

37

CD-CLK O Serial clock signal output to the CXD3017Q (IC101)

38

CD-POWER O CD power on/off control signal output “L”: on, “H”: off

39 CLOCK-OUT

O Clock signal output terminal Not used (open)

40

HOLD O Automatic power control hold signal output to the CXA2581N (IC103)

41

M-RESET O Micom reset signal output to the liquid crystal display driver (IC601) “L”: reset

42

XLT O Serial data latch pulse output to the CXD3017Q (IC101)

43

XRST O CD reset signal output to the CXD3017Q (IC101) and BA5974FM (IC102) “L”: reset

44

LOAD-IN O Turn motor control signal output to the BA6956AN (IC701)

6-23. IC PIN FUNCTION DESCRIPTION

Loading...

Loading...