www.ti.com

3

SLOU489–August 2017

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

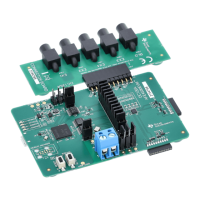

AFE5832 32-Channel Analog Front-End Evaluation Module (EVM Rev. A)

63 EVM ADC Clock Source Configuration Examples..................................................................... 52

64 CPLD Switches and LEDs ................................................................................................ 53

65 HSDC Pro Trigger Configuration for SW................................................................................ 54

66 HSDC Pro Trigger Configuration for SW Trigger ...................................................................... 55

67 HSDC Pro Trigger Configuration for HW................................................................................ 55

68 HSDC Pro Trigger Configuration for HW External Trigger ........................................................... 56

69 AFE5832 EVM Block Diagram ........................................................................................... 58

70 AFE5832 Rev. A EVM Schematic 1 of 12 .............................................................................. 59

71 AFE5832 Rev. A EVM Schematic 2 of 12 .............................................................................. 60

72 AFE5832 Rev. A EVM Schematic 3 of 12 .............................................................................. 61

73 AFE5832 Rev. A EVM Schematic 4 of 12 .............................................................................. 62

74 AFE5832 Rev. A EVM Schematic 5 of 12 .............................................................................. 63

75 AFE5832 Rev. A EVM Schematic 6 of 12 .............................................................................. 64

76 AFE5832 Rev. A EVM Schematic 7 of 12 .............................................................................. 65

77 AFE5832 Rev. A EVM Schematic 8 of 12 .............................................................................. 66

78 AFE5832 Rev. A EVM Schematic 9 of 12 .............................................................................. 67

79 AFE5832 Rev. A EVM Schematic 10 of 12............................................................................. 68

80 AFE5832 Rev. A EVM Schematic 11 of 12............................................................................. 69

81 AFE5832 Rev. A EVM Schematic 12 of 12............................................................................. 70

82 Read DDR Error for No Capture ......................................................................................... 82

List of Tables

1 Default Header Configuration Table Rev. A ............................................................................ 50

2 EVM Rev. A Testpoints ................................................................................................... 50

3 AFE5832 EVM Bill of Materials .......................................................................................... 71

Trademarks

Microsoft Windows 7, Windows 10 are registered trademarks of Microsoft Corporation.

National Instruments is a registered trademark of National Instruments Corporation.

Python is a registered trademark of Python Software Foundation.

Xilinx is a trademark of Xilinx Incorporated.

All other trademarks are the property of their respective owners.