wire Serial Configuration and Data Interface

is configured via a simple 4

is the slave. This interface is

ad and write buffered data. All

All transactions on the SPI interface start with

a header byte containing a

pin must be kept low during transfers

transfer of a header byte or during read/write

from/to a register, the transfer will be

g for the address and data

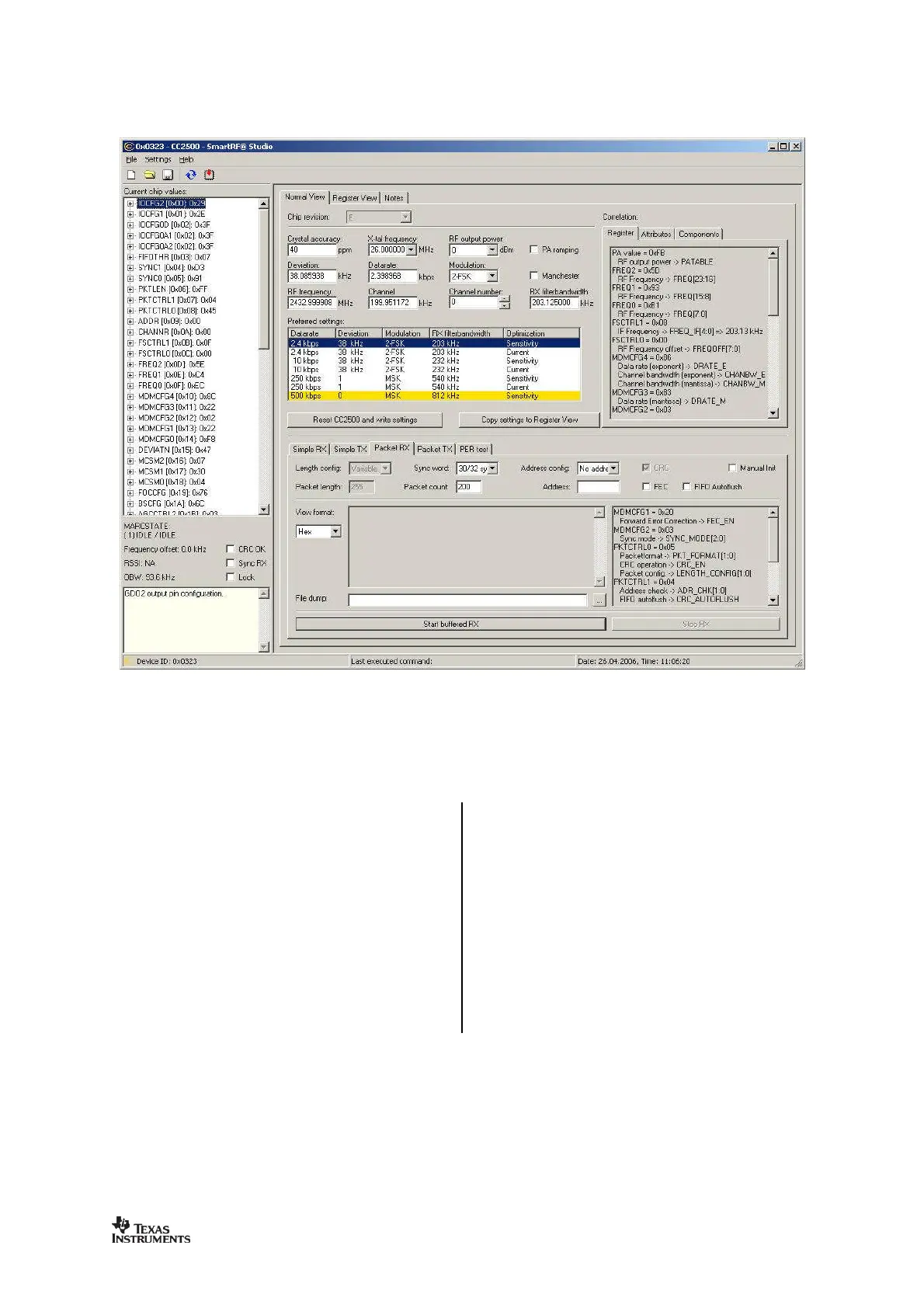

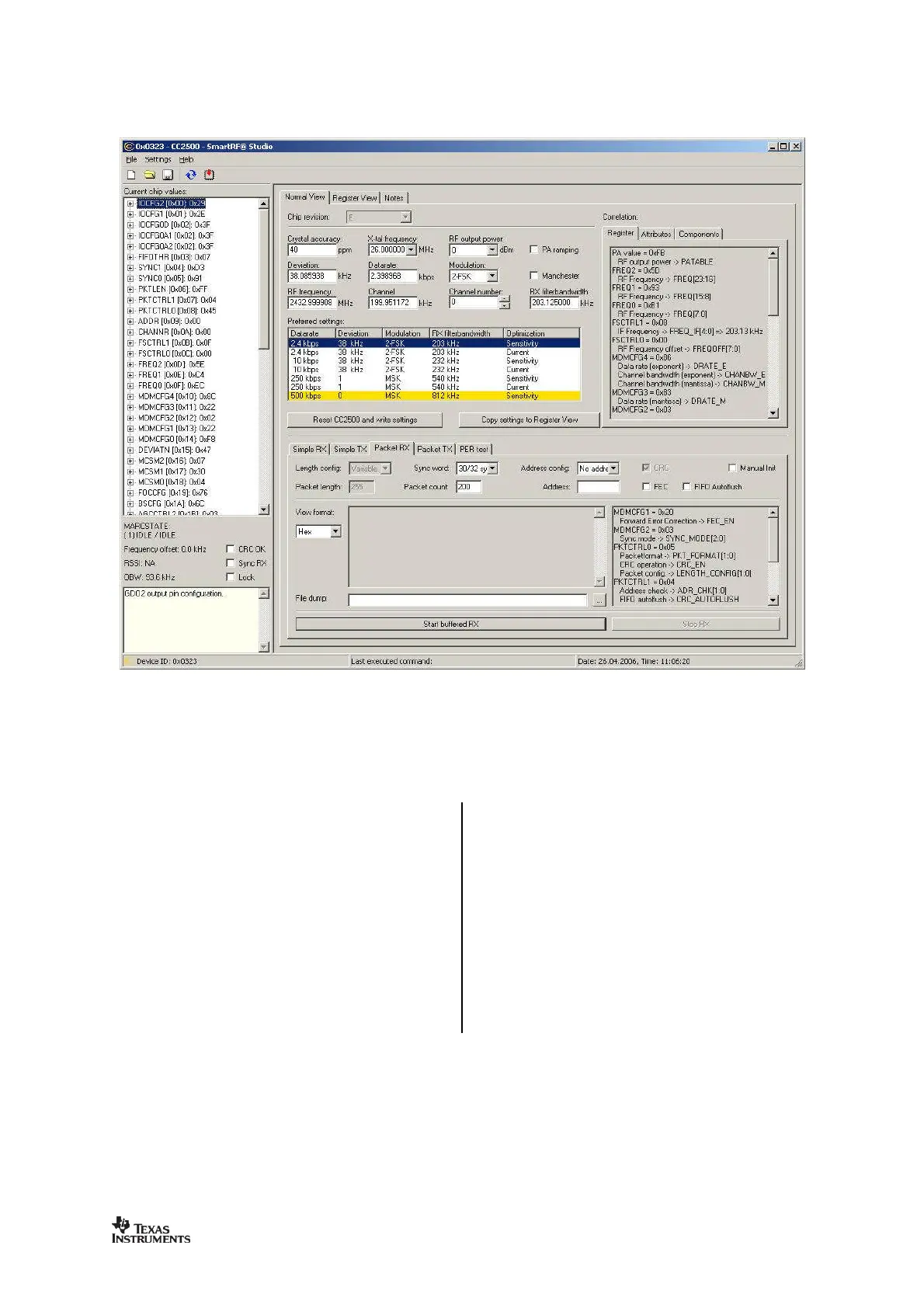

transfer on the SPI interface is shown in

is pulled low, the MCU must wait

transfer the header byte. This indicates that

the crystal is running. Unless the chip was in

the SLEEP or XOFF states, the

always go low immediately after taking

Loading...

Loading...