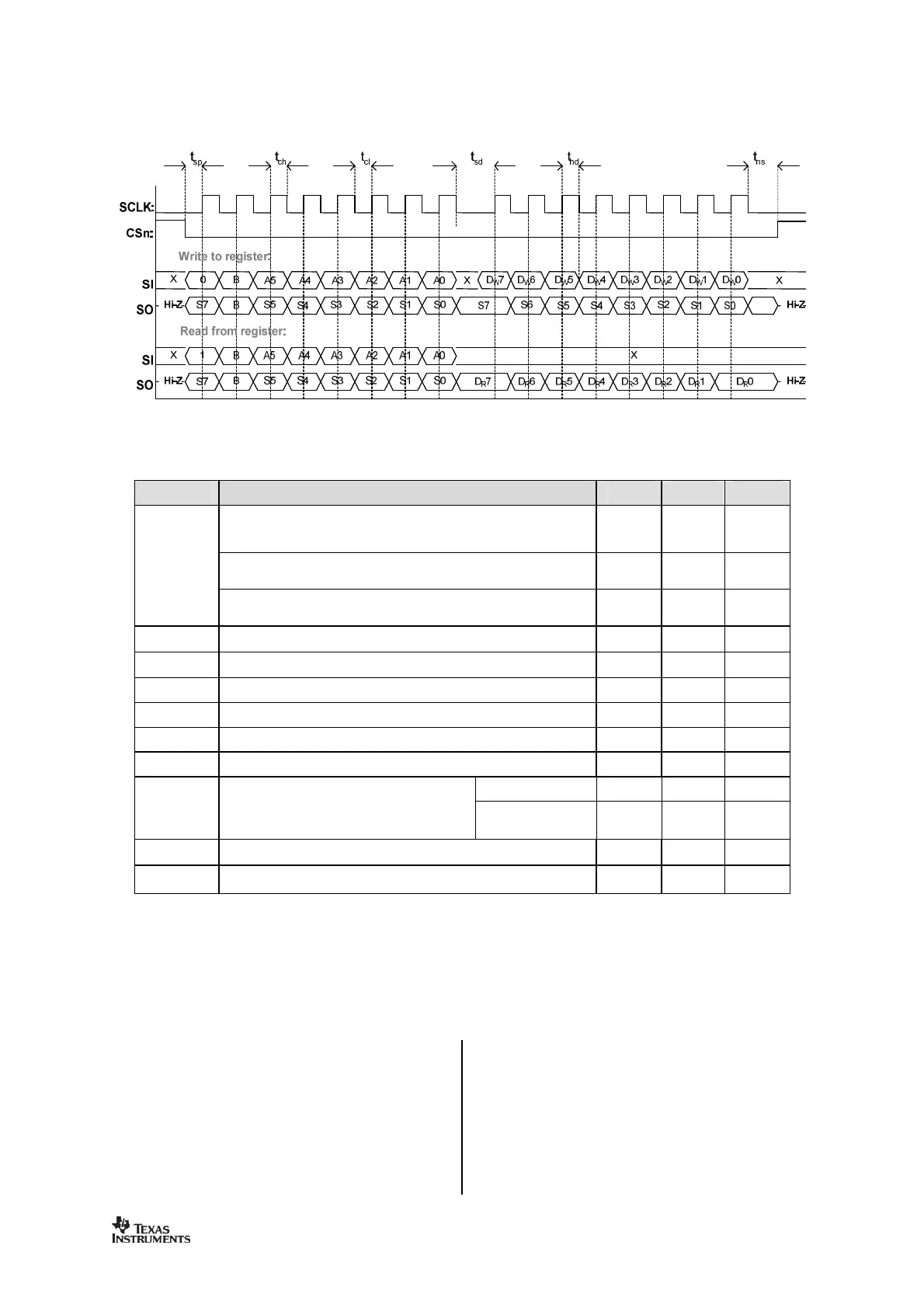

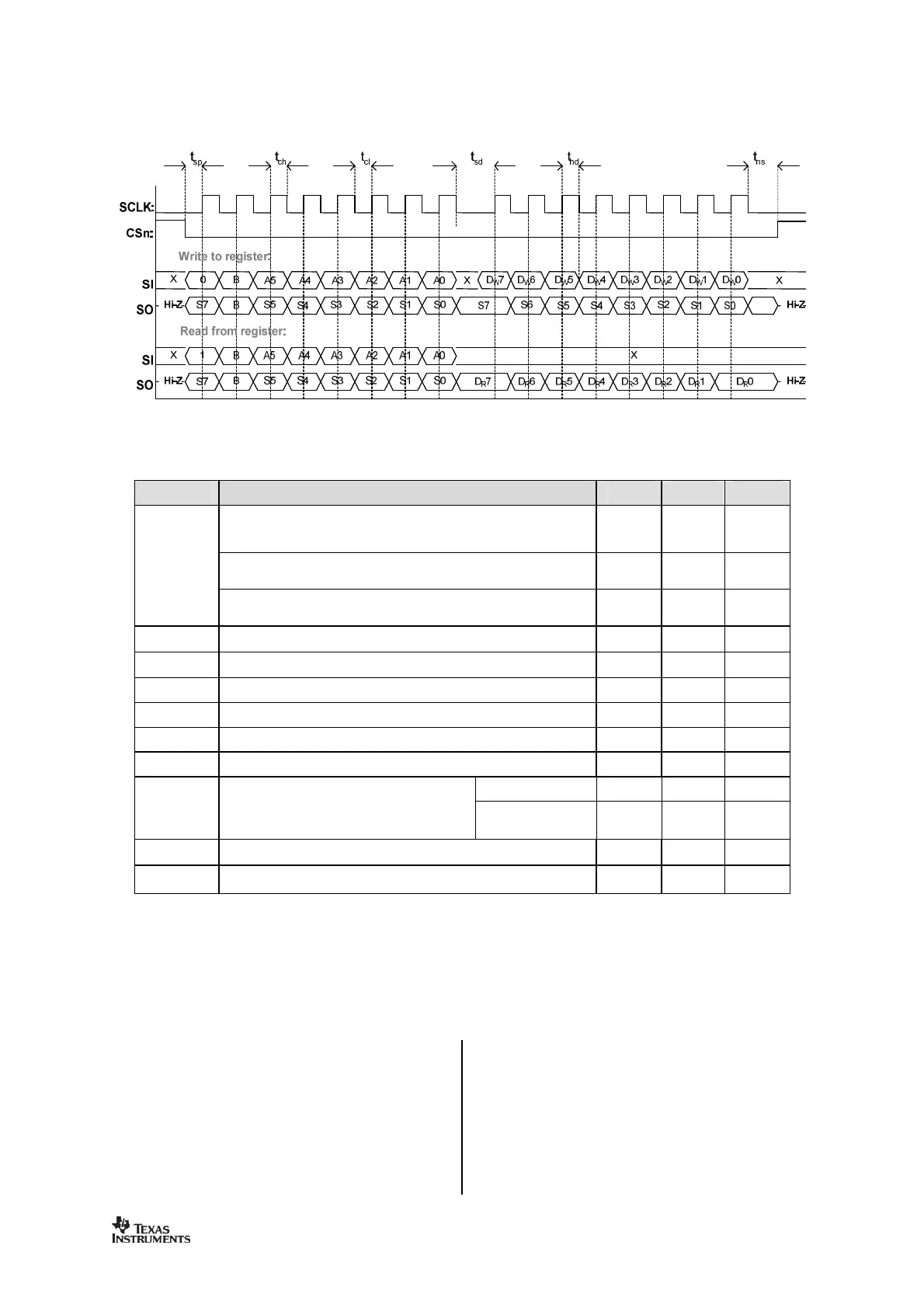

100 ns delay inserted between address byte and data byte (single access), or between

address and data, and between each data byte (burst access).

No delay between address and data byte

No delay between address and data byte, or between data bytes

applies between address and d

Hold data after positive edge on

can be used in cases where the user does not read the

up time of the crystal being used.

is the crystal oscillator

measured on CC2500EM reference design

When the header byte, data byte or

strobe is sent on the SPI interface, the chip

status byte is sent by the

pin. The status byte contains key status

e MCU. The first bit, s7, is

signal; this signal must go low

before the first positive edge of

signal indicates that the crystal is

This value reflects the state of the chip. The

XOSC and power to the digital core is on in

the IDLE state, but all other modules are in

power down. The frequency and channel

Loading...

Loading...