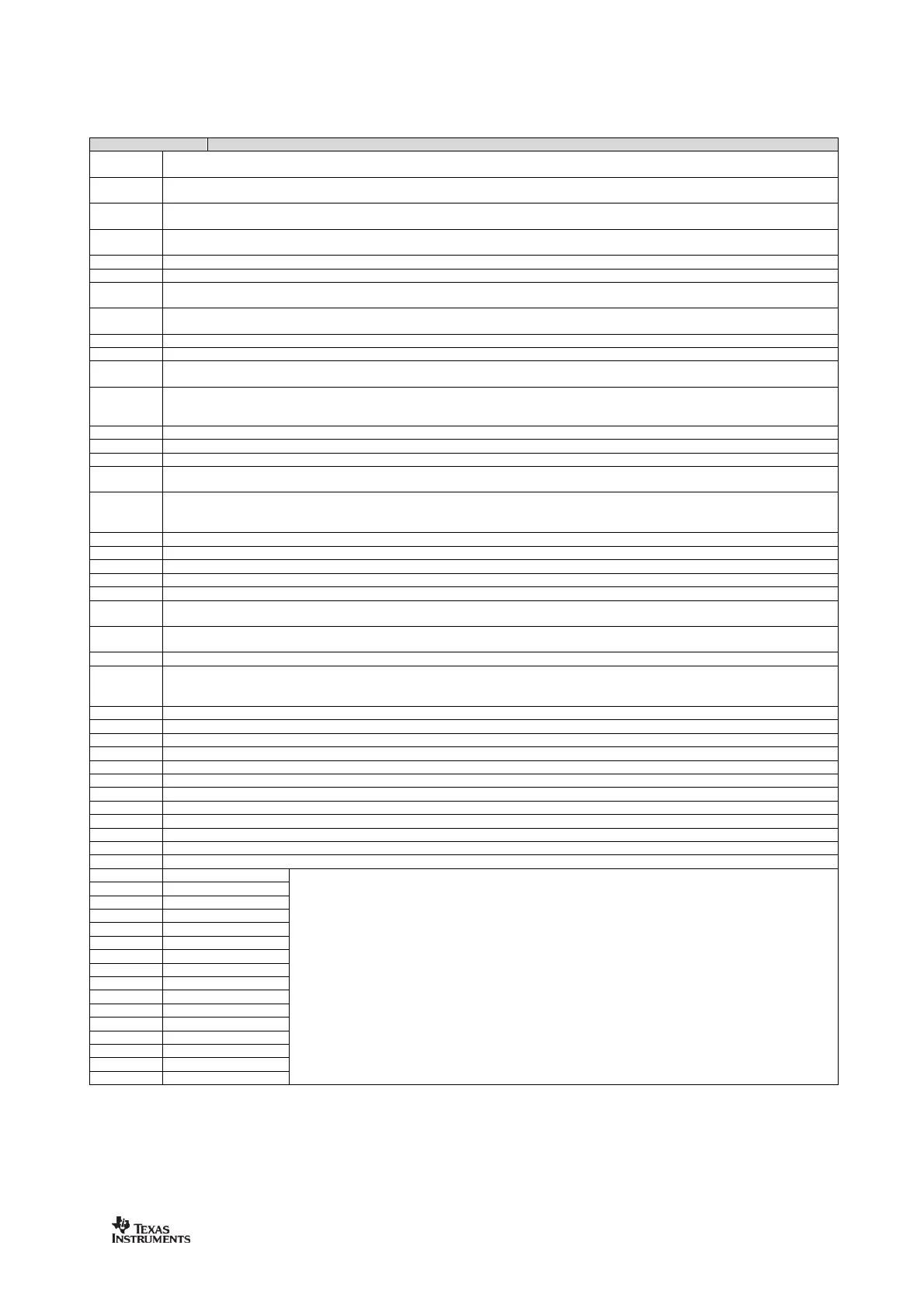

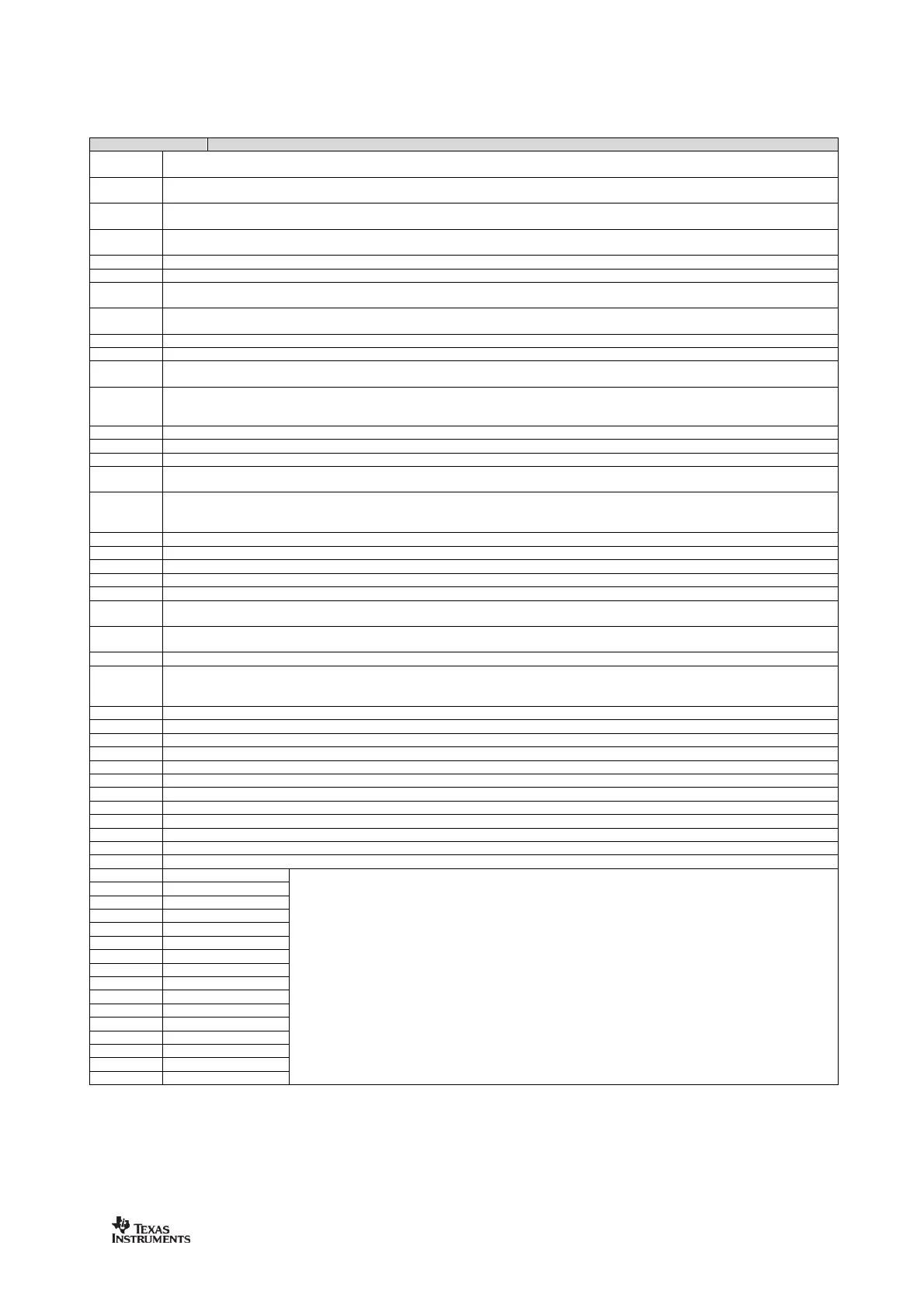

Associated to the RX FIFO: Asserts when RX FIFO is filled at or above the RX FIFO threshold. D

FIFO is drained below the same threshold.

Associated to the RX FIFO: Asserts when RX FIFO is filled at or above the RX FIFO threshold or the end of packet is

asserts when the RX FIFO is empty.

o the TX FIFO: Asserts when the TX FIFO is filled at or above the TX FIFO threshold. De

TX FIFO is below the same threshold.

Associated to the TX FIFO: Asserts when TX FIFO is full. De

asserts when the TX FIFO is drained below th

Asserts when the RX FIFO has overflowed. De

asserts when the FIFO has been flushed.

Asserts when the TX FIFO has underflowed. De

asserts when the FIFO is flushed.

Asserts when sync word has been sent / rece

asserts at the end of the packet. In RX, the pin will de

when the optional address check fails or the RX FIFO overflows. In TX the pin will de

assert if the TX FIFO underflows.

Asserts when a packet has been received with CRC

asserts when the first byte is read from the RX FIFO. Only

Preamble Quality Reached. Asserts when the PQI is above the programmed PQT value.

Clear channel assessment. High when RSSI level is below

threshold (dependent on the current CCA_MODE setting)

. The PLL is in lock if the lock detector output has a positive transition or is constantly logic high. To

check for PLL lock the lock detector output should be used as an

Serial Clock. Synchronous to the data in synchronous serial mode.

ata is set up on the falling edge

In TX mode, data is sampled by

on the rising edge of the serial clock w

Serial Synchronous Data Output (DO). Used for synchronous serial mode.

Serial Data Output. Used for asynchronous serial mode.

Carrier sense. High if RSSI level is above threshold.

st CRC comparison matched. Cleared when entering/restarting RX mode. Only valid if

Can be used together with RX_SYMBOL_TICK for alternative serial RX ou

Can be used together with RX_SYMBOL_TICK for alternative serial RX output.

PA_PD. Note: PA_PD will h

ave the same signal level in SLEEP and TX states. To control an external PA or RX/TX

switch in applications where the SLEEP state is used it is recommended to use

LNA_PD. Note: LNA_PD will have

the same signal level in SLEEP and RX states. To control an external LNA or RX/TX

switch in applications where the SLEEP state is used it is recommended to use

ther with RX_HARD_DATA for alternative serial RX output.

_Z_EN_N. When this output is 0,

is configured as input (for serial TX data).

to 0 (HW1 achieved by setting

control an external LNA/PA or RX/TX switch.

There are 3 GDO pins, but o

CLK_XOSC/n can be selected as an output at any

C/n is to be monitored on one of the GDO pins, the other two GDO pins must

be configured to values less than 0x30.

default value is CLK_XOSC/192.

Loading...

Loading...