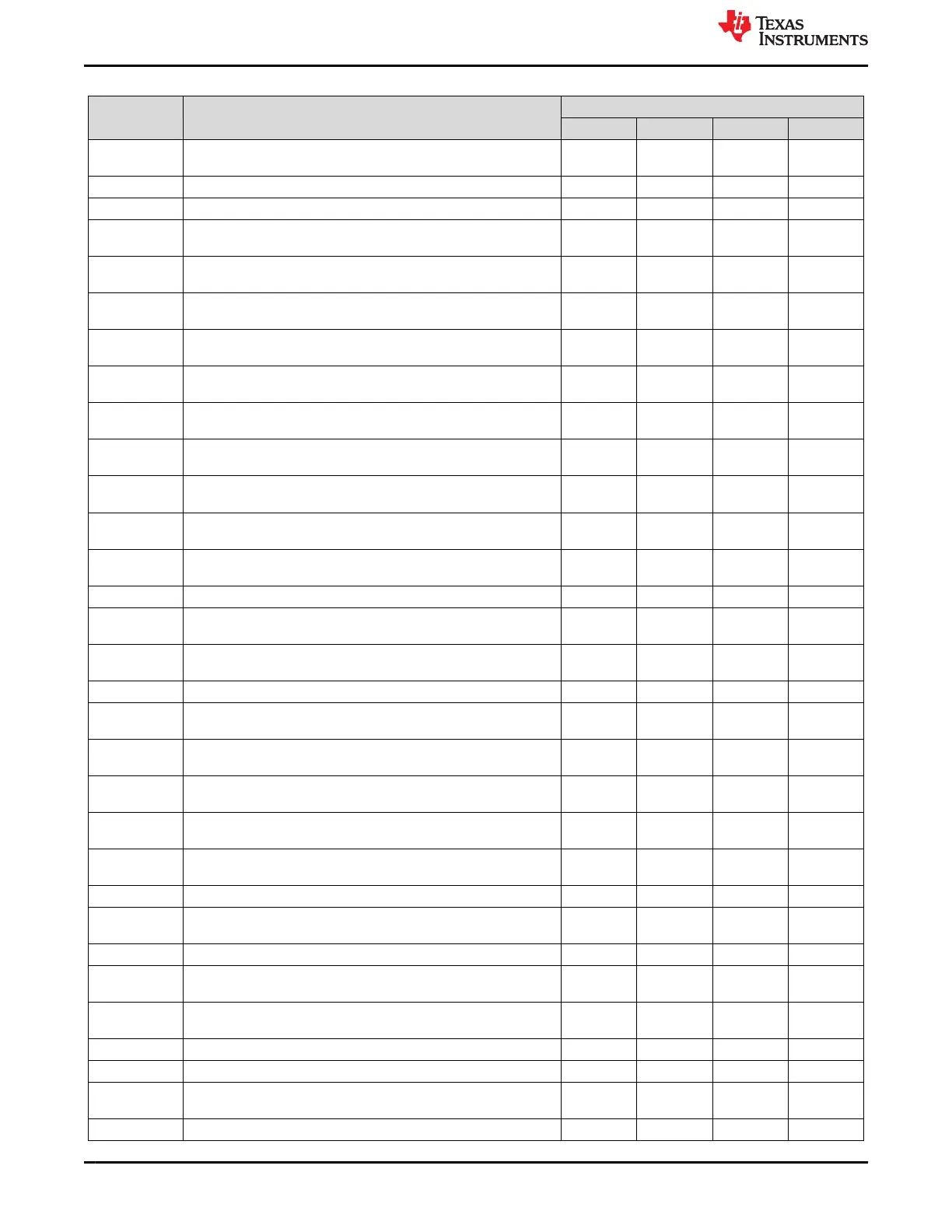

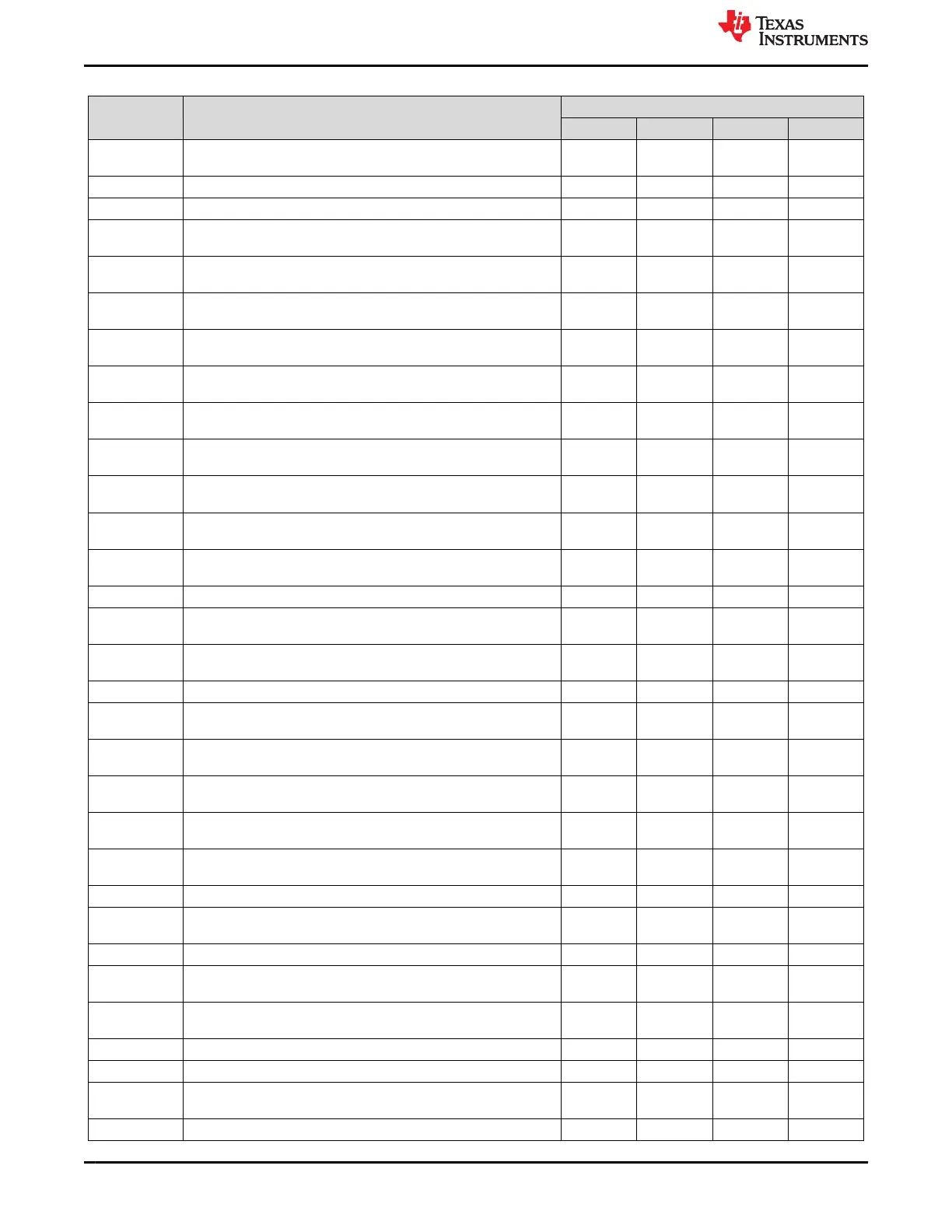

Table 1-2. Advisories Matrix (continued)

MODULE DESCRIPTION

SILICON REVISIONS AFFECTED

0 A B C

eQEP eQEP: Position Counter Incorrectly Reset on Direction Change

During Index

Yes Yes Yes Yes

eQEP eQEP: eQEP Inputs in GPIO Asynchronous Mode Yes Yes Yes Yes

PLL PLL: May Not Lock on the First Lock Attempt Yes Yes Yes Yes

PLL PLL: Power Down and Bypass May Take up to 120 SYSCLK

Cycles to be Effective

Yes Yes Yes Yes

SDFM SDFM: Data Filter Output Does Not Saturate at Maximum Value

With Sinc3 and OSR = 256

Yes Yes Yes Yes

SDFM SDFM: Spurious Data Acknowledge Event When Data Filter is

Configured and Enabled for the First Time

Yes Yes Yes Yes

SDFM SDFM: Spurious Data Acknowledge Event When Data Filter is

Synchronized Using PWM FILRES Signal

Yes Yes Yes Yes

SDFM SDFM: Comparator Filter Module may Generate Spurious Over-

Value and Under-Value Conditions

Yes Yes Yes Yes

SDFM SDFM: Dynamically Changing Threshold Settings (LLT, HLT), Filter

Type, or COSR Settings Will Trigger Spurious Comparator Events

Yes Yes Yes Yes

SDFM SDFM: Dynamically Changing Data Filter Settings (Such as Filter

Type or DOSR) Will Trigger Spurious Data Acknowledge Events

Yes Yes Yes Yes

SDFM SDFM: Manchester Mode (Mode 2) Does Not Produce Correct

Filter Results Under Several Conditions

Yes Yes Yes Yes

FPU FPU: FPU-to-CPU Register Move Operation Preceded by Any FPU

2p Operation

Yes Yes Yes Yes

FPU FPU: LUF, LVF Flags are Invalid for the EINVF32 and EISQRTF32

Instructions

Yes Yes Yes Yes

Memory Memory: Prefetching Beyond Valid Memory Yes Yes Yes Yes

INTOSC INTOSC: V

DDOSC

Powered Without V

DD

Can Cause INTOSC

Frequency Drift

Yes Yes Yes Yes

Low-Power

Modes

Low-Power Modes: Power Down Flash or Maintain Minimum

Device Activity

Yes Yes Yes Yes

I2C I2C: SDA and SCL Open-Drain Output Buffer Issue Yes Yes Yes Yes

ePWM ePWM: An ePWM Glitch can Occur if a Trip Remains Active at the

End of the Blanking Window

Yes Yes Yes Yes

ePWM ePWM: ePWM Dead-Band Delay Value Cannot be Set to 0 When

Using Shadow Load Mode for RED/FED

Yes Yes Yes Yes

ePWM ePWM: Trip Events Will Not be Filtered by the Blanking Window for

the First 3 Cycles After the Start of a Blanking Window

Yes Yes Yes Yes

SYSTEM SYSTEM: Multiple Successive Writes to CLKSRCCTL1 Can Cause

a System Hang

Yes Yes Yes Yes

CMPSS CMPSS: COMPxLATCH May Not Clear Properly Under Certain

Conditions

Yes Yes Yes Yes

CMPSS CMPSS: Ramp Generator May Not Start Under Certain Conditions Yes Yes Yes Yes

CMPSS CMPSS: CMPIN4N, CMPIN4P, CMPIN5N, and CMPIN5P Not

Available

Yes Yes

GPIO GPIO: Open-Drain Configuration May Drive a Short High Pulse Yes Yes Yes Yes

GPIO GPIO: GPIO0–GPIO7, GPIO46, GPIO47 Shunt to V

SS

Due to Fast

Transients at High Temperature

Yes Yes

During DCAN FIFO Mode, Received Messages May be Placed Out

of Order in the FIFO Buffer

Yes Yes Yes Yes

Boot ROM Boot ROM: Calling SCI Bootloader from Application Yes Yes Yes Yes

Boot ROM Boot ROM: Using CPU1 Wait Boot or CPU2 Idle Mode Yes Yes Yes Yes

Boot ROM Boot ROM: Device Will Hang During Boot if X1 Clock Source is not

Present

Yes

HRPWM HRPWM: HRCNFG Register Reads and Bit-Wise Writes Yes Yes

Usage Notes and Advisories Matrices www.ti.com

4 TMS320F2837xD Dual-Core Real-Time MCUs Silicon Errata (Silicon

Revisions C, B, A, 0)

SPRZ412M – DECEMBER 2013 – REVISED MARCH 2023

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

Loading...

Loading...