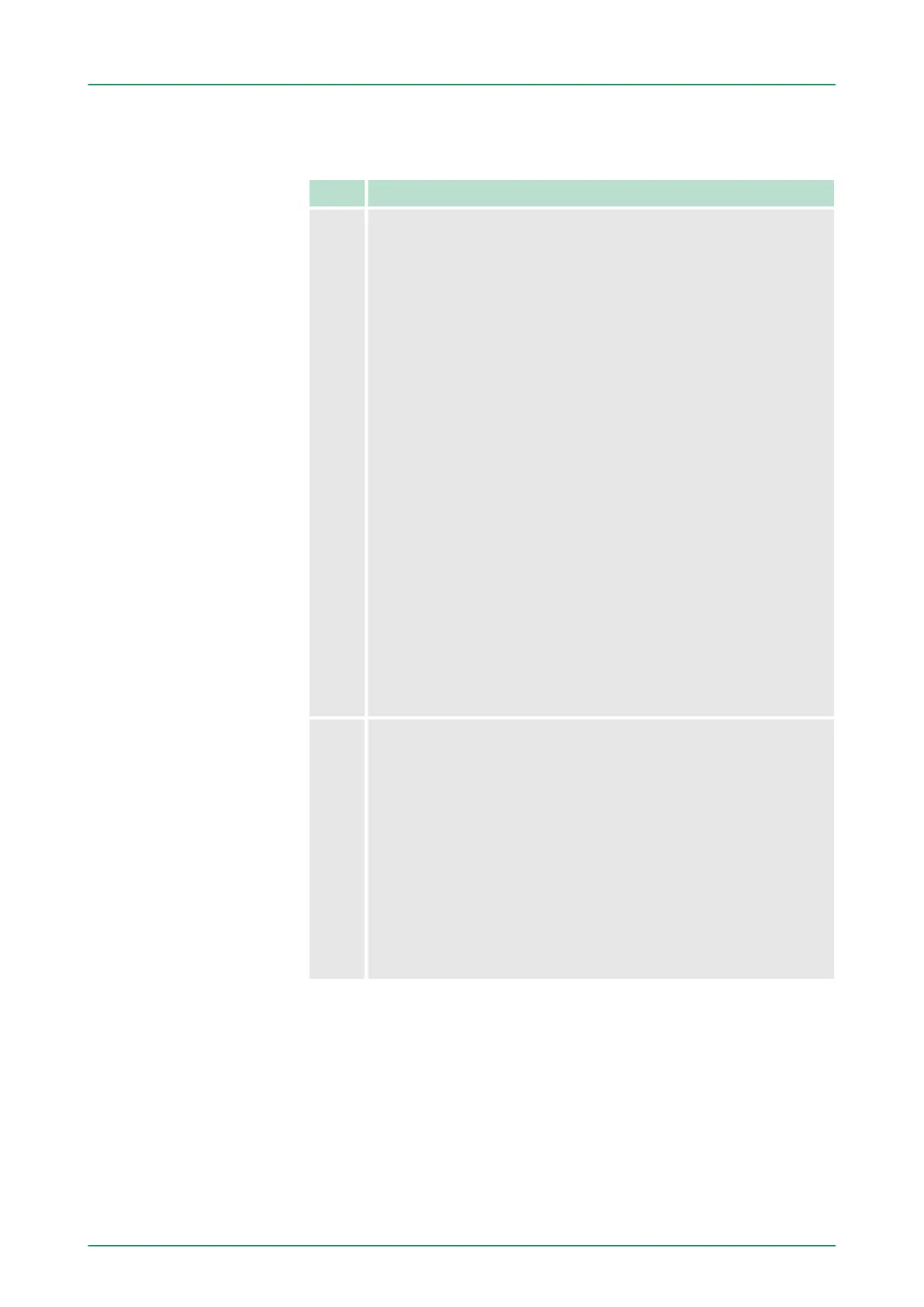

The double word for the counter mode has the following struc-

ture:

Byte Bit 7 ... 0

0

n Bit 2 ... 0: Signal evaluation

–

000b = Counter de-activated

At de-activated counter the further parameter settings for

this counter are ignored and the according I/O channel is

set as "normal" output if this should be used as output.

– 001b = Encoder 1-tier (at counter

X

(A

X

) and counter

X

(B

X

))

– 010b = Encoder 2-tier (at counter

X

(A

X

) and counter

X

(B

X

))

– 011b = Encoder 4-tier (at counter

X

(A

X

) and counter

X

(B

X

))

– 100b = Pulse/direction (pulse at counter

X

(A

X

) and direc-

tion at counter

X

(B

X

))

n Bit 6 ... 3: C

X

Input (function of the counter input as gate, latch

or reset)

– 0000b = de-activated (counter starts at set SW gate)

– 0001b = Gate

X

The input of counter

X

serves as gate. High level at gate

activates the HW gate. The counter may only start when

HW and SW gate are set.

– 0010b = Monoflop *

– 0100b = Latch

X

(edge 0-1 at input saves counter value of

counter

X

)

– 1000b = Reset

X

(positive level at input resets counter

X

)

n Bit 7: Gate function (internal gate)

– 0 = abort (count process starts again at load value)

– 1 = interrupt (count process continues with counter value)

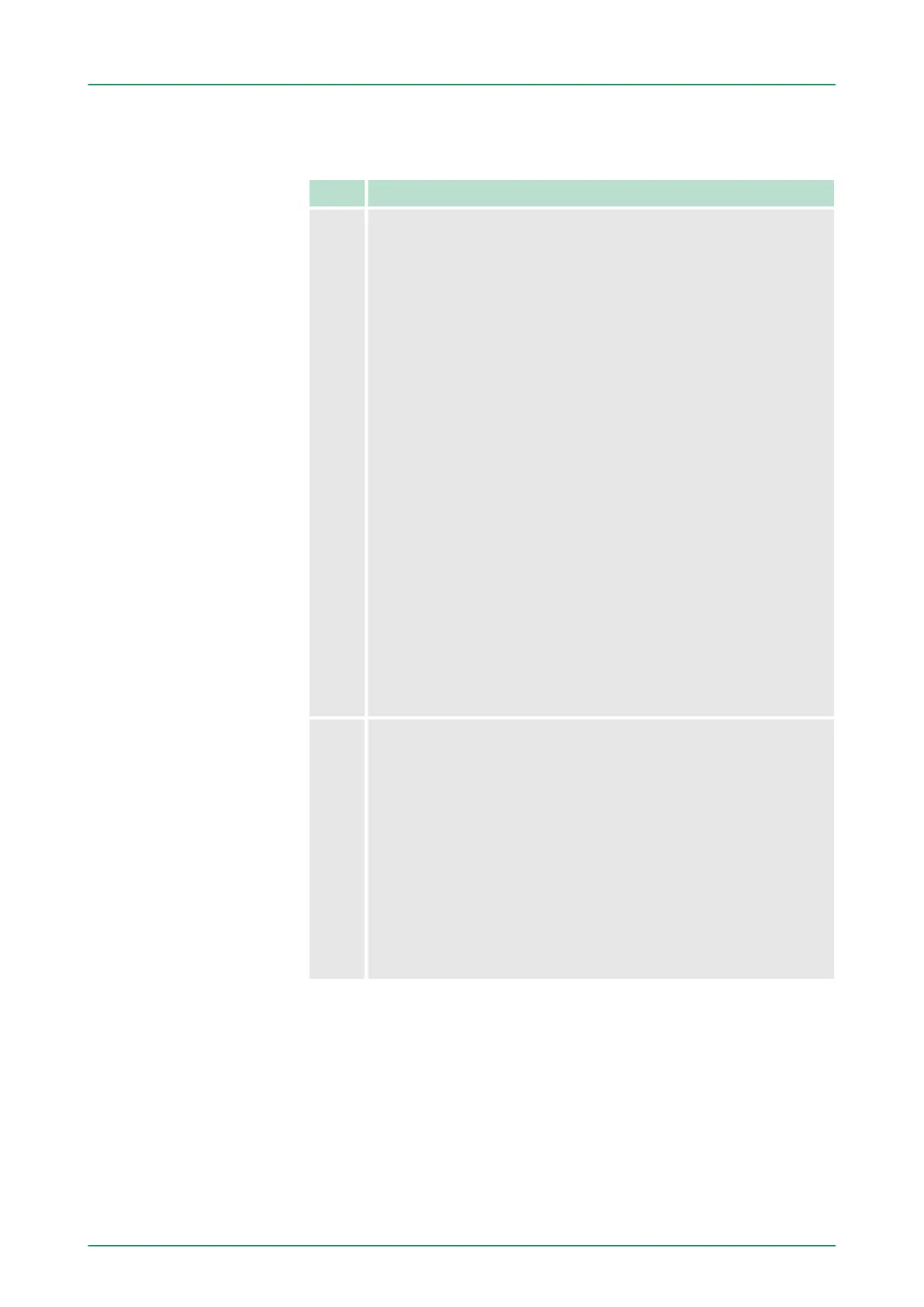

1

n Bit 2 ... 0: Output set

(OUT

X

of counter

X

is set when condition is met)

–

000b = never

– 001b = counter value ³ comparison value

– 010b = counter value £ comparison value

– 100b = counter value = comparison value

n Bit 3: Count direction

– 0 = Count direction inverted: OFF (count direction at B

X

not inverted)

– 1 = Count direction inverted: ON (count direction at B

X

inverted)

n Bit 7 ... 4: reserved

VIPA System 300SDeployment I/O periphery

Counter - Parametrization

HB140 | CPU | 314-6CF03 | GB | 16-43 154

Loading...

Loading...