6-5

IM 701310-17E

Status Reports

6.4 Extended Event Register

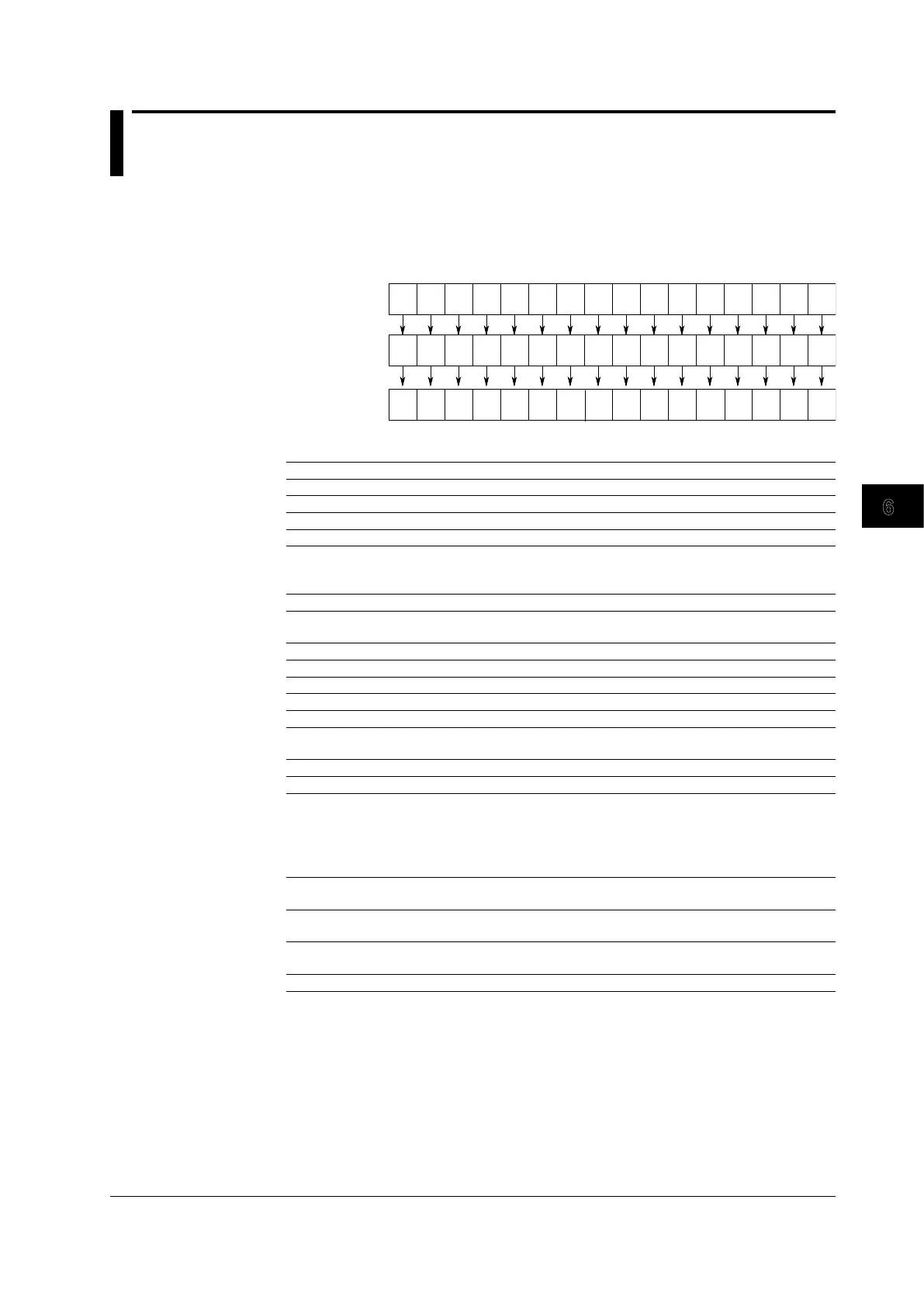

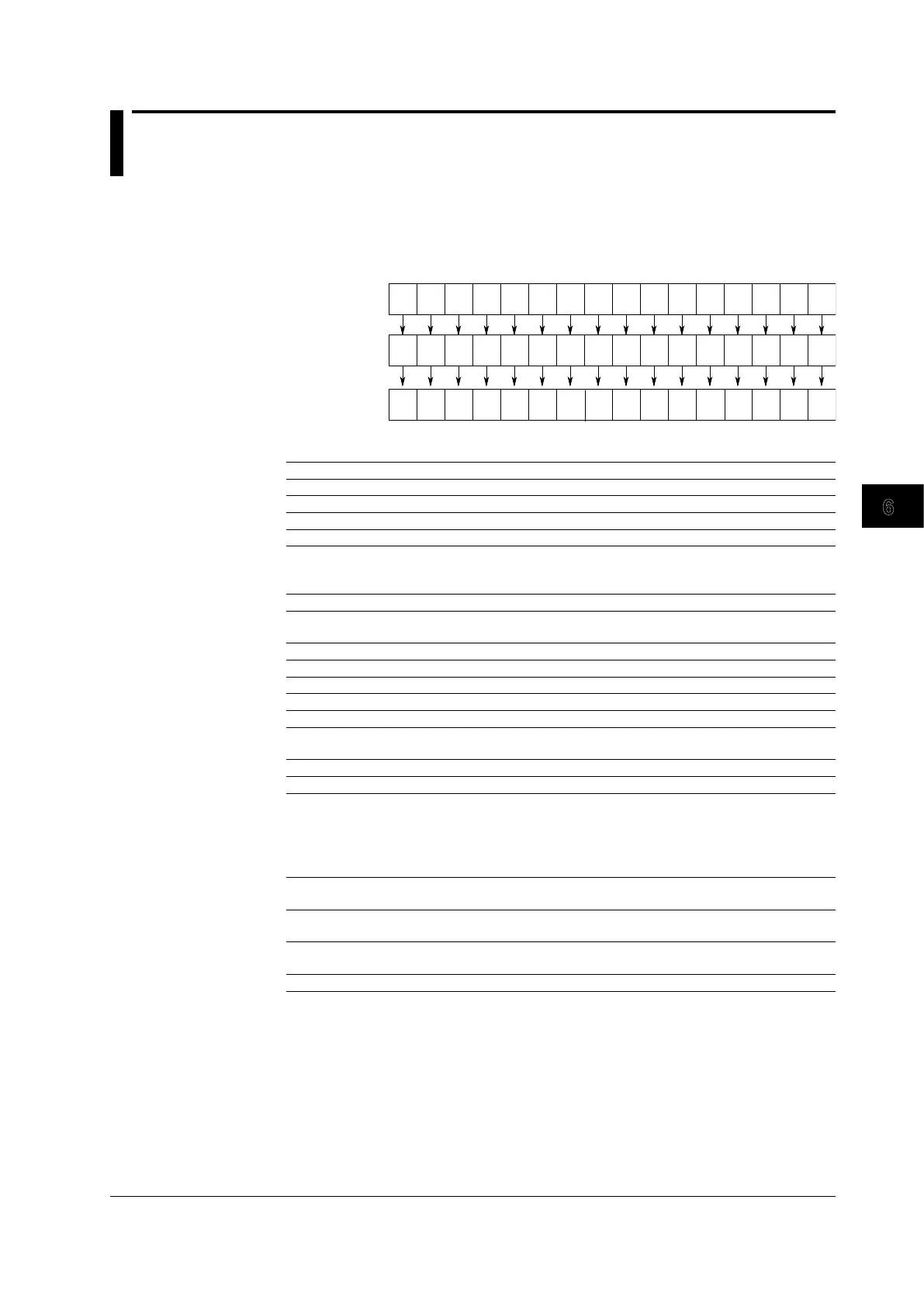

Reading the extended event register tells you whether changes in the condition register

(reflecting internal conditions) have occurred. A filter can be applied which allows you to

decide which events are reported to the extended event registe.

ACS

6

HST

7 5 4 3 2 1 0

PRN TST CAL TRG CUR RUNNGOSCH

8

UME

9

MES

1011

TEL

12

NSG

13

AN1

14

AN2

15

67 5 4 3 2 1 089101112131415

Condition register

:STATus:CONDition?

Transition filter

01415

Extended event register

1

67 5 4 38910111213

2

67 5 4 3 2 189101112131415

16

:STATus:FILTer<x>

{RISE|FALL|BOTH|NEVer}

:STATus:EESR?

FILTer<x>→

The meaning of each bit of the condition register is as follows:

Bit 0 RUN (Running) Set to 1 while waveform acquisition is in progress.

Bit 1 CUR (Cursor) Set to 1 during cursor measurement.

Bit 2 TRG (Awaiting trigger) Set to 1 when waiting for a trigger.

Bit 3 CAL (Calibration) Set to 1 while calibration is in progress.

Bit 4 TST (Testing) Set to 1 while self-test is in progress.

Bit 5 PRN (Printing) Set to 1 while the built-in printer is operating, while data is

being output to an external printer (USB/network), or while

screen image data is being saved.

Bit 6 ACS (Accessing) Set to 1 while a storage drive is being accessed.

Bit 7 MES (Measuring) Set to 1 when automated measurement of waveform

parameters is in progress.

Bit 8 HST (History Search) Set to 1 while history search is in progress.

Bit 9 UME (User Math Executing) Set to 1 while the user-defined computation is in progress.

Bit 10 NGO (Go/No-go) Set to 1 while GO/NO-GO search is in progress.

Bit 11 SCH (Search) Set to 1 while search is in progress.

Bit 12 TEL (Telecom Test) Set to 1 while the telecom test is in progress.

Bit 13 NSG (N-Single) Set to 1 while continuous acquisition is in progress when the

trigger mode is set to single (N).

Bit 14 AN1 (Analysis1) Set to 1 while Analysis 1 is in progress.

Bit 15 AN2 (Analysis2) Set to 1 while Analysis 2 is in progress.

The transition filter parameters detect changes in the specified bit (numerical suffix, 1 to

16) of the condition register in the following manner and overwrite the extended event

register.

RISE The specified bit of the extended event register is set to 1 when the bit of the condition

register changes from 1 to 0.

FALL The specified bit of the extended event register is set to 1 when the bit of the condition

register changes from 0 to 1.

BOTH The bit of the extended event register is set to 1 when the bit of the condition register

changes from 0 to 1 or from 1 to 0.

NEVer Always 0.

Loading...

Loading...