Theory of Operation 8

16901A Logic Analysis System Service Guide 93

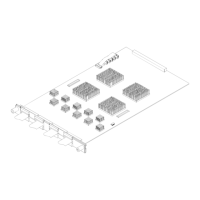

CPU motherboard via the PCI board. It also performs power

distribution and numerous interconnects. The MIB has two

module bus FPGAs.

Module Bus FPGA(s)

The Xilinx XC3S500E FPGA is the primary bridge between

the CPU and the measurement modules. It effectively

performs a translation from PCI slot to the proprietary

module interface bus.

In the 2- slot, high- power frame, a second module FPGA,

Xilinx XC2VP20, performs the translation from PCI slot to a

second, high- speed module interface bus.

I/O FPGA

The Xilinx XC2V250 FPGA is the center of the instrument

I/O functions. The system interfaces directly to this part in

the same way it talks to the measurement module slot(s), via

a 16- bit multiplexed general purpose bus. The FPGA is

loaded from an on board EPROM at power up. The EPROM

contents can be changed (updated) through the system

software via a JTAG port.

A major function of this FPGA component is system

correlation; time alignment of the measurement modules and

possible other modules connected through the multiframe

port or Trigger In connector. This is done with eight 52-bit

counters running at 1.6 GHz, allowing relative time

alignment of eight seperate events. A 100 MHz clock is also

selected from three possible sources (internal, multiframe,

external) and a synchronizing signal is generated for time

alignment across multiframe.

A second major function of the FPGA is the logical

combination and routing of the module arm and trigger

lines: ARM, TRIG, FLAG. These signals are used by the

modules to start and stop each other in addition to

supplying the signals for real- time correlation.

The other FPGA functions include a system interface to

control the Trigger In and Trigger Out ports, a serial DAC

programmer, and UARTs for multiframe.

Multiframe Input/Output Multiframe is a proprietary bus used

to connect multiple 16900A, 16901A, and 16902A frames. It

physically consists of two connectors (input, output) which

cable frames together in a daisy chain configuration. It

logically allows two or more frames to appear and operate

Loading...

Loading...