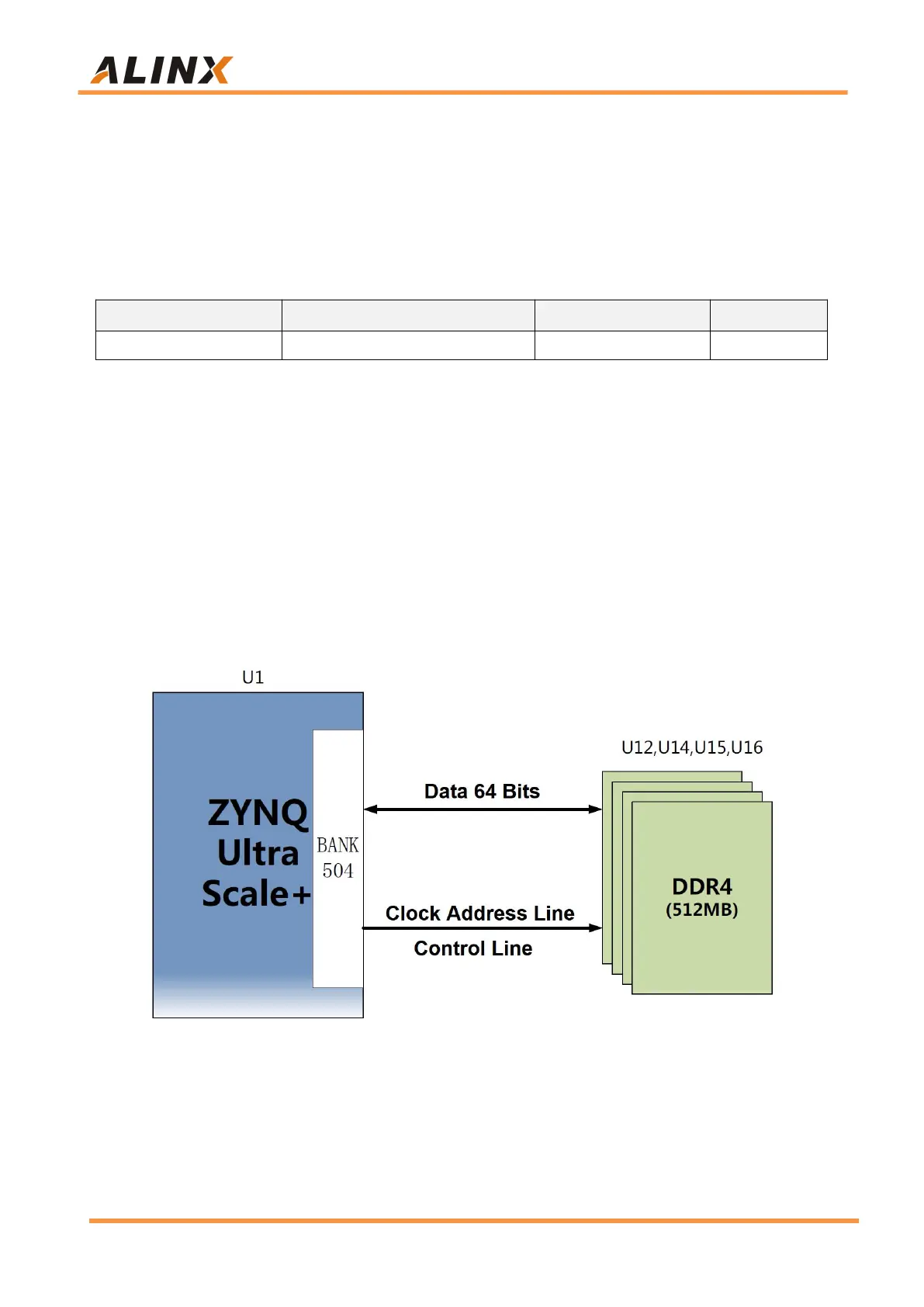

are directly connected to the memory interface of the PS BANK504. The

highest operating speed of the DDR4 SDRAM on the PL side can reach

1066MHz (data rate 2133Mbps), and four DDR4 storage systems are directly

connected to the memory interface of PS's BANK504. The specific

configuration of DDR4 SDRAM is shown in Table 2-3-1 below:

Table 2-3-1: DDR4 SDRAM Configuration

The hardware design of DDR4 requires strict consideration of signal

integrity. We have fully considered the matching resistor/terminal resistance,

trace impedance control, and trace length control in circuit design and PCB

design to ensure high-speed and stable operation of DDR4.

The hardware connection of DDR4 SDRAM on the PS Side is shown in

Figure 2-3-1:

Figure 2-3-1: DDR4 DRAM schematic diagram on the PS Side

Loading...

Loading...