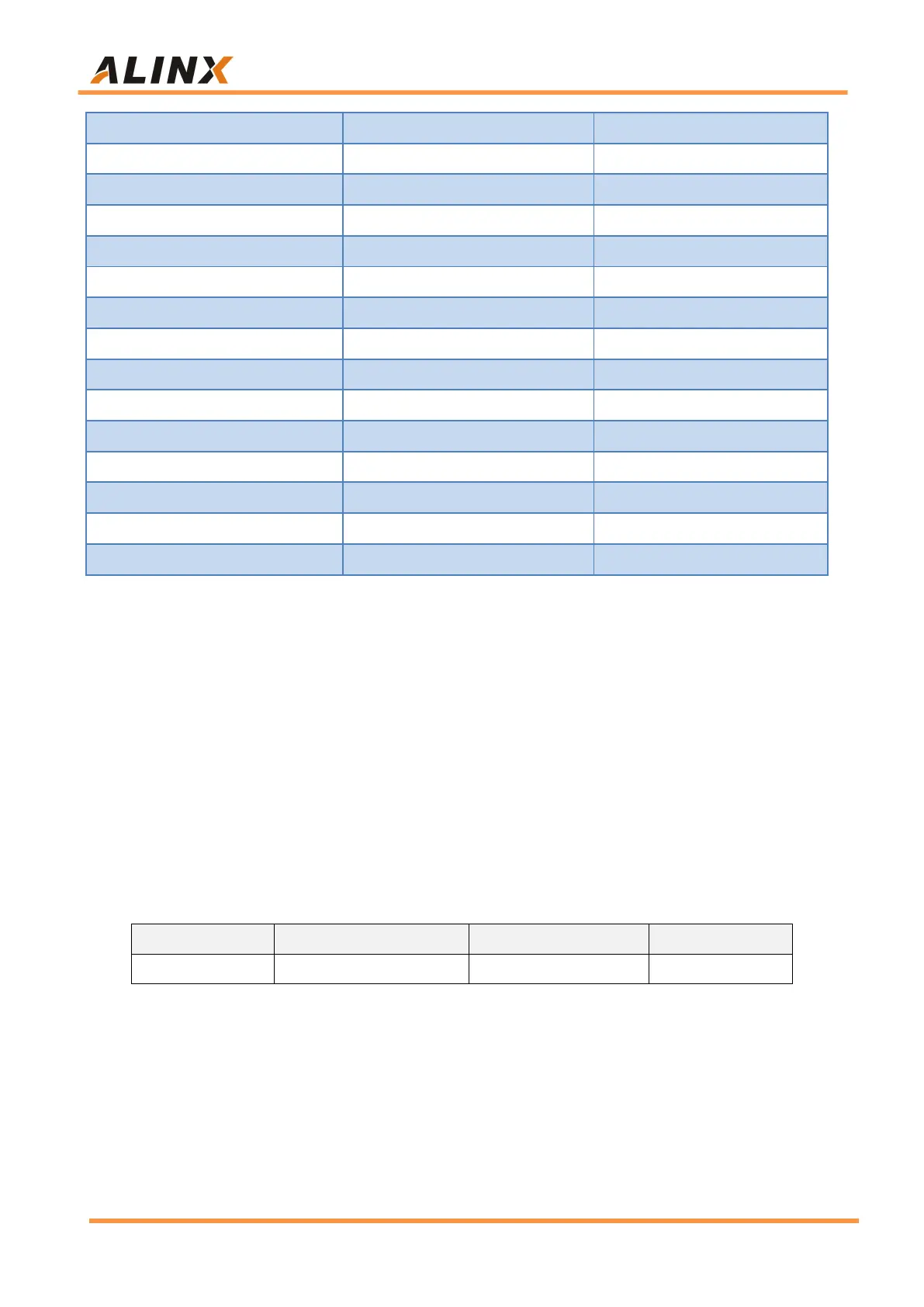

Part 2.4: QSPI Flash

The FPGA core board ACU2CG is equipped with one 256MBit Quad-SPI

FLASH chip to form an 8-bit bandwidth data bus, the flash model is

MT25QU256ABA1EW9, which uses the 1.8V CMOS voltage standard. Due to

the non-volatile nature of QSPI FLASH, it can be used as a boot device for the

system to store the boot image of the system. These images mainly include

FPGA bit files, ARM application code, and other user data files. The specific

models and related parameters of QSPI FLASH are shown in Table 2-4-1.

Table 2-4-1: QSPI FLASH Specification

QSPI FLASH is connected to the GPIO port of the BANK500 in the PS

section of the ZYNQ chip. In the system design, the GPIO port functions of

these PS ports need to be configured as the QSPI FLASH interface. Figure

Loading...

Loading...