Note: If the HSMC loopback adapter is mounted, the I2C_SCL will be directly routed back

to I2C_SDA. Because audio chip, TV decoder chip and HSMC share one I2C bus, therefore

audio and video chip won’t function correctly.

Table 4-24 TV Decoder Pin Assignments

4

4

.

.

1

1

6

6

I

I

m

m

p

p

l

l

e

e

m

m

e

e

n

n

t

t

i

i

n

n

g

g

a

a

T

T

V

V

E

E

n

n

c

c

o

o

d

d

e

e

r

r

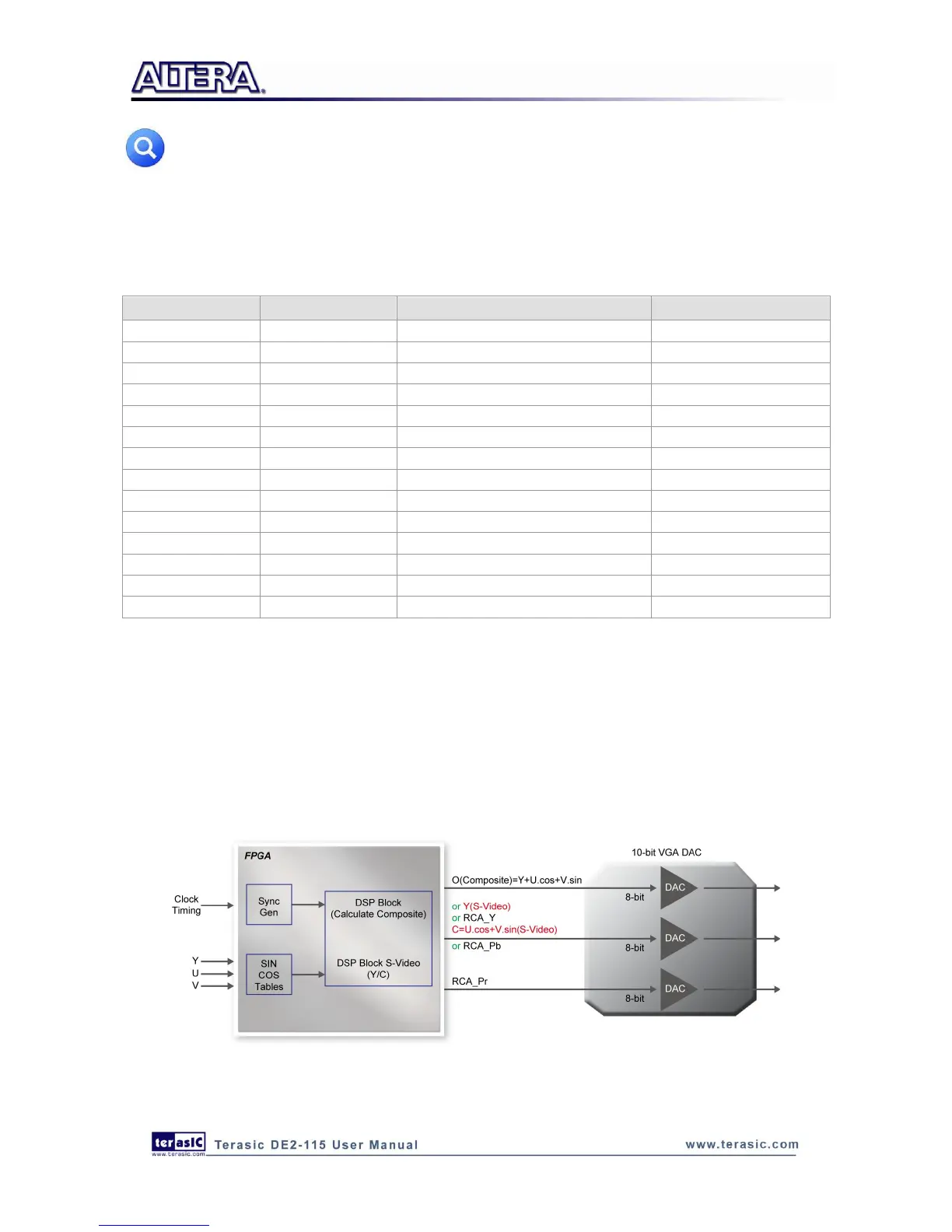

Although the DE2-115 board does not include a TV encoder chip, the ADV7123 (10-bit high-speed

triple ADCs) can be used to implement a professional-quality TV encoder with the digital

processing part implemented in the Cyclone IV E FPGA. Figure 4-30 shows a block diagram of a

TV encoder implemented in this manner.

Figure 4-30 A TV Encoder that uses the Cyclone IV E FPGA and the ADV7123

Loading...

Loading...