VI SDRAM CONTROLLER BLOCK: SDRAM INTERFACE

S1C33L03 FUNCTION PART EPSON B-VI-2-11

A-1

B-VI

SDRAM

Timing setup

The following parameters can be set in conformity with SDRAM specifications before use.

Table 2.10 SDRAM Parameters

Symbol SDRAM parameter

Set values

(# of clocks)

Control bits

tRC ACTIVE to ACTIVE command period 1 to 8 SDRTRC[2:0] (D[2:0])/SDRAM

AUTO REFRESH command period timing set-up register 1 (0x39FFC4)

Exit SELF REFRESH to ACTIVE command period

tRAS ACTIVE to PRECHARGE command period 1 to 8 SDRTRAS[2:0] (D[7:5])/SDRAM

Minimum SELF REFRESH period timing set-up register 1 (0x39FFC4)

tRCD ACTIVE to READ or WRITE delay time 1 to 4 SDRTRCD[1:0] (D[7:6])/SDRAM

timing set-up register 2 (0x39FFC5)

tRP PRECHARGE command period 1 to 4 SDRTRP[1:0] (D[4:3])/SDRAM

timing set-up register 1 (0x39FFC4)

tRRD ACTIVE bank (a) to ACTIVE bank (b) period 1 to 4 SDRTRRD[1:0] (D[4:3])/SDRAM

timing set-up register 2 (0x39FFC5)

tRSC MODE REGISTER SET cycle time 1 or 2 SDRTRSC (D5)/SDRAM timing set-

up register 2 (0x39FFC5)

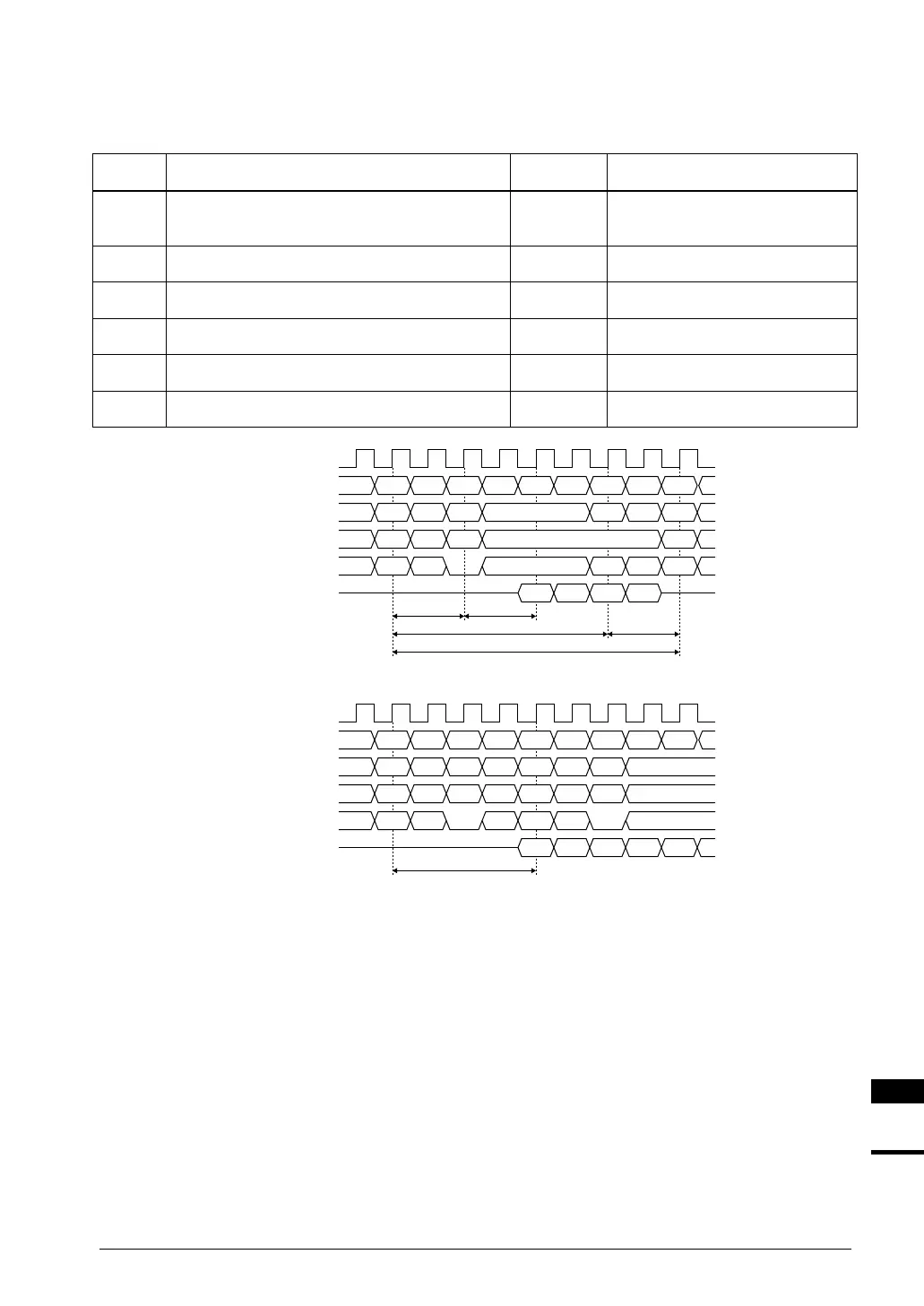

BCLK

Command

SDBA[1:0]

SDA[12:11, 9:0]

SDA10

DQ[15:0]

ACTVNOP NOP NOP NOP NOP PREREAD

BA BA

ROW COL

ROW

BA

ROW

ROW

DATA DATA DATA DATA

t

RCD

t

RAS

t

RC

t

RP

CAS latency

(Burst length = 4)

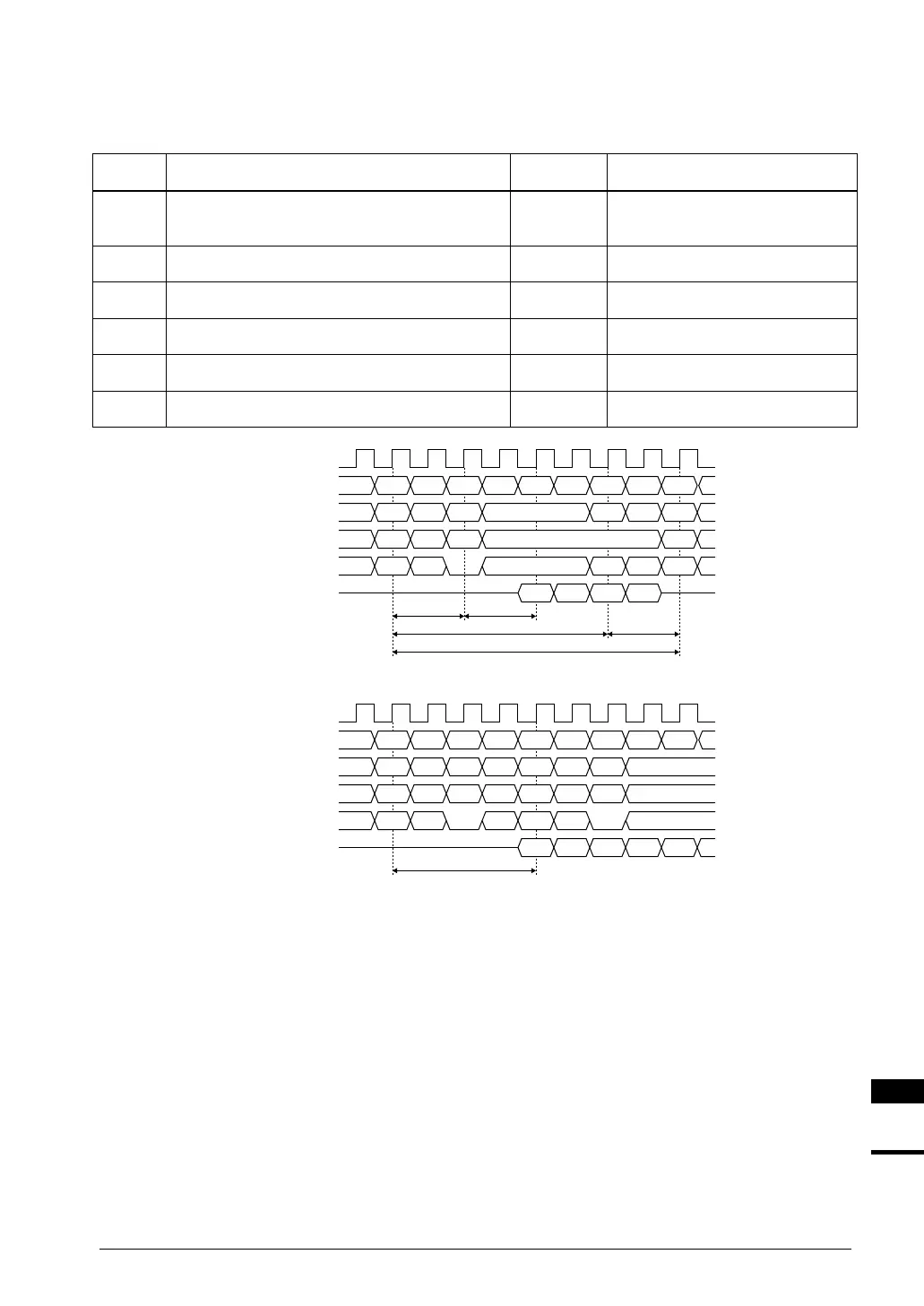

NOP ACTV

BA

BKsel

BCLK

Command

SDBA[1:0]

SDA[12:11, 9:0]

SDA10

DQ[15:0]

ACTVNOP NOP NOP ACTV NOP READREAD

BAa BAa

ROWa COLa

BAb

ROWb

ROWa ROWb

COLb

Da DbDa

+1

Da

+2

Da

+3

t

RRD

(Burst length = 4)

(a) Burst read

(b) Bank interleaved access

NOP NOP

BAb

Figure 2.7 SDRAM Parameters

Note:When the auto-refresh command is executed, the following command may be issued 3 or 4

CPU_CLK cycles from that point regardless of the t

RC value set in the SDRTRC[2:0]

(D[2:0])/SDRAM timing set-up register 1 (0x39FFC4). Therefore, use SDRAMs with 75 ns or less

of t

RC.

Loading...

Loading...