Chapter 2. IBM eX5 technology 19

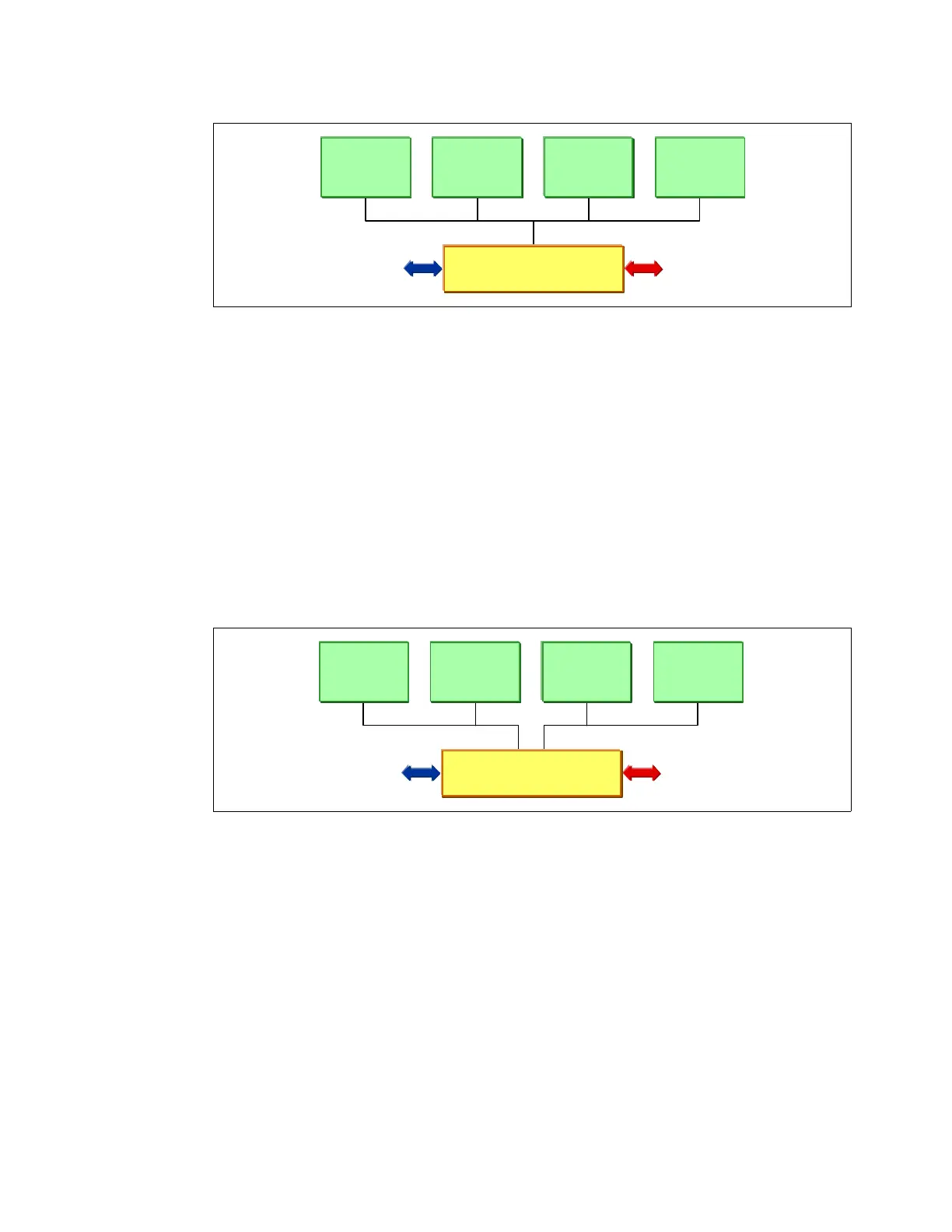

Figure 2-1 Shared front-side bus, in the IBM x360 and x440; with snoop filter in the x365 and x445

The front-side bus carries all reads and writes to the I/O devices, and all reads and writes to

memory. Also, before a processor can use the contents of its own cache, it must know

whether another processor has the same data stored in its cache. This process is described

as

snooping the other processor’s caches, and it puts a lot of traffic on the front-side bus.

To reduce the amount of cache snooping on the front-side bus, the core chip set can include a

snoop filter, which is also referred to as a cache coherency filter. This filter is a table that

keeps track of the starting memory locations of the 64-byte chunks of data that are read into

cache, called

cache lines, or the actual cache line itself, and one of four states: modified,

exclusive, shared, or invalid (MESI).

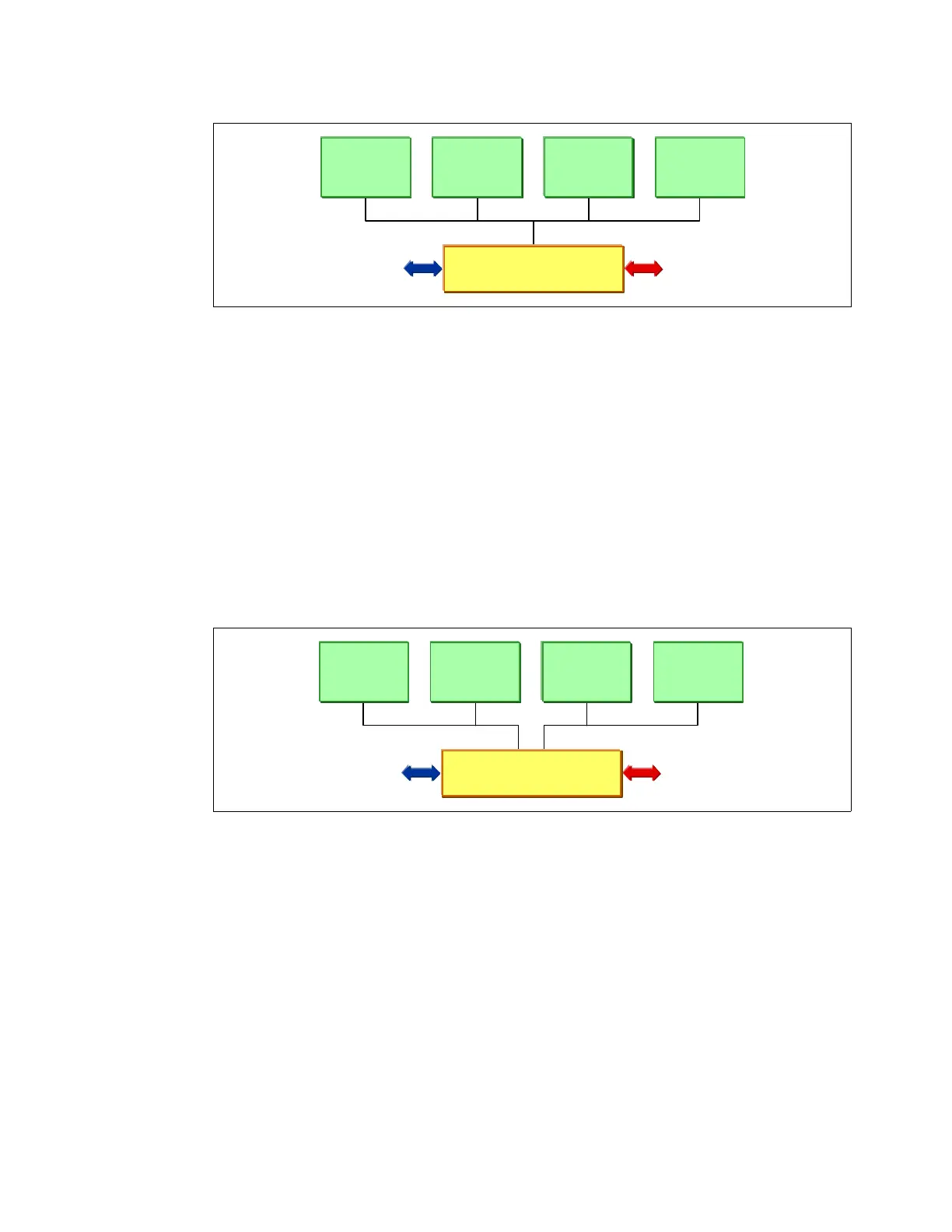

The next step in the evolution was to divide the load between a pair of front-side buses, as

shown in Figure 2-2. Servers that implemented this design include the IBM System x3850

and x3950 (the

M1 version).

Figure 2-2 Dual independent buses, as in the x366 and x460 (later called the x3850 and x3950)

This approach had the effect of reducing congestion on each front-side bus, when used with a

snoop filter. It was followed by independent processor buses, shown in Figure 2-3 on

page 20. Servers implementing this design included the IBM System x3850 M2 and x3950

M2.

Memory I/O

Processor ProcessorProcessor Processor

Core Chip set

Memory I/O

Processor ProcessorProcessor Processor

Core Chip set

Loading...

Loading...