20 IBM eX5 Implementation Guide

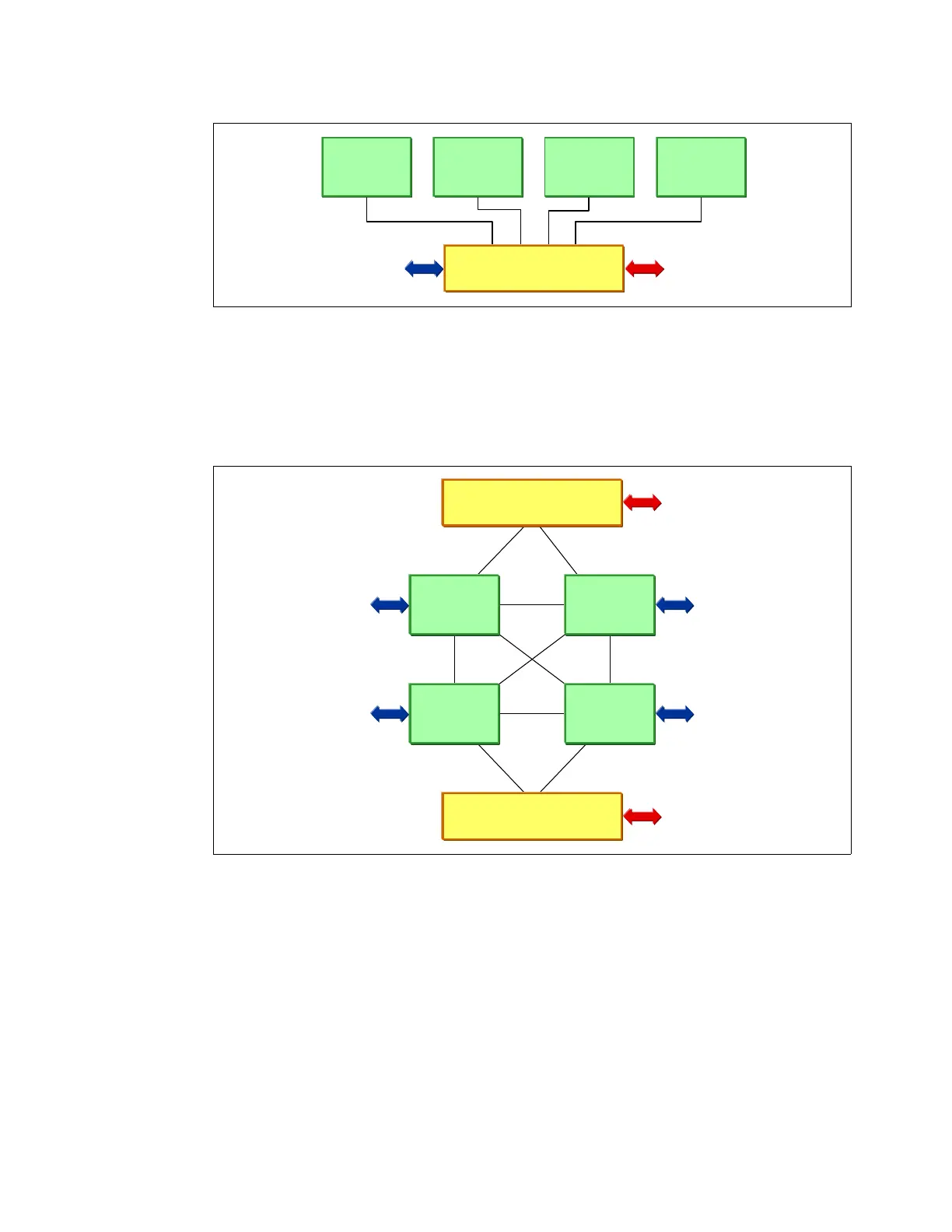

Figure 2-3 Independent processor buses, as in the x3850 M2 and x3950 M2

Instead of a parallel bus connecting the processors to a core chip set, which functions as both

a memory and I/O controller, the Xeon 6500 and 7500 family processors implemented in IBM

eX5 servers include a separate memory controller to each processor. Processor-to-processor

communications are carried over shared-clock, or

coherent QPI links, and I/O is transported

over

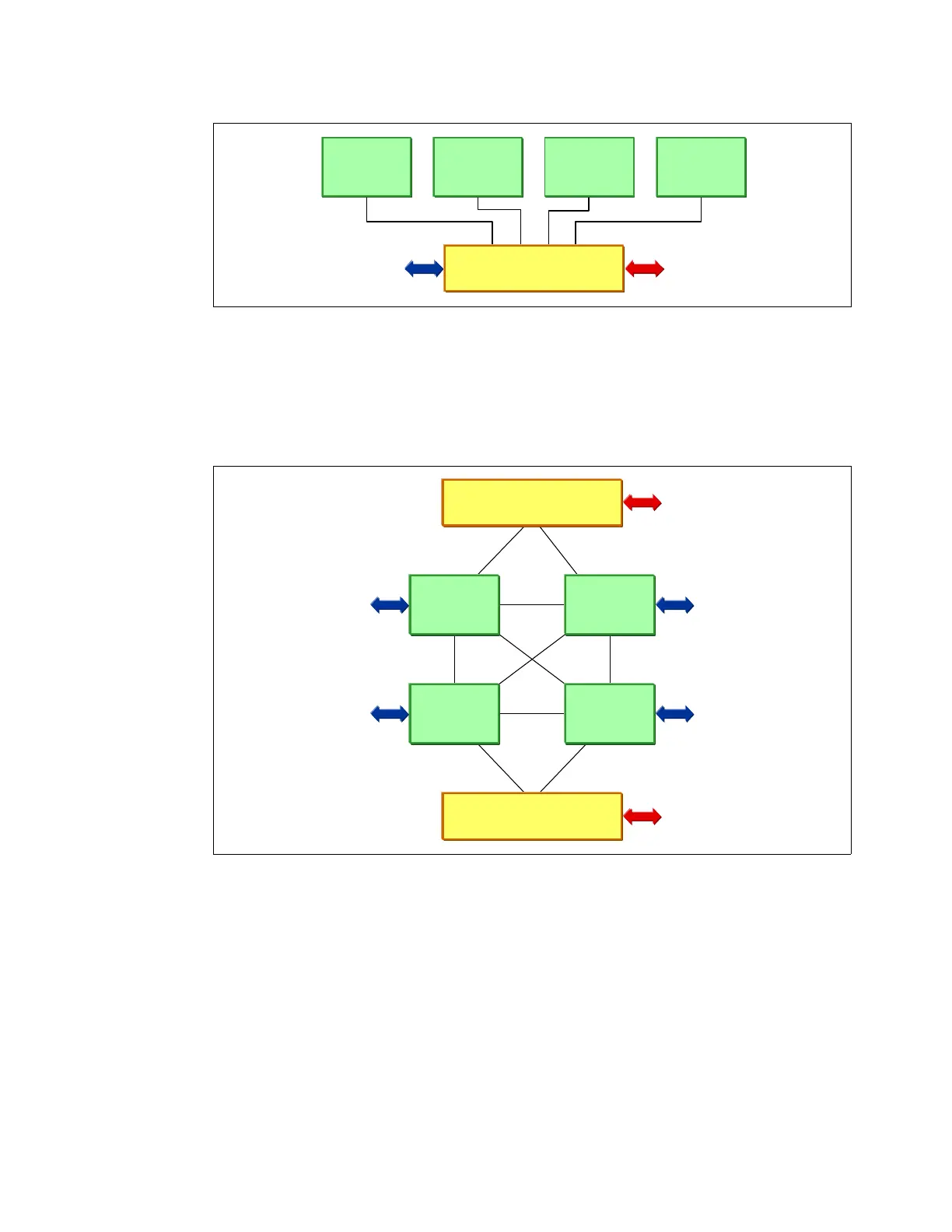

non-coherent QPI links through I/O hubs. Figure 2-4 shows this information.

Figure 2-4 Figure 2-4 QPI, as used in the eX5 portfolio

In previous designs, the entire range of memory was accessible through the core chip set by

each processor, a shared memory architecture. This design creates a non-uniform memory

access (NUMA) system, in which part of the memory is directly connected to the processor

where a given thread is running, and the rest must be accessed over a QPI link through

another processor. Similarly, I/O can be local to a processor, or remote through another

processor.

For QPI use, Intel has modified the MESI cache coherence protocol to include a forwarding

state, so when a processor asks to copy a shared cache line, only one other processor

responds.

For more information about QPI, go to the following website:

http://www.intel.com/technology/quickpath/

Memory I/O

Processor ProcessorProcessor Processor

Core Chip set

I/O Hub

Processor Processor

Processor Processor

I/O Hub

Memory

I/O

I/O

Memory

Memory Memory

Loading...

Loading...