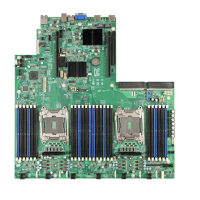

Intel® Server Board S3420GP TPS Functional Architecture

Revision 2.4

Intel order number E65697-010

25

PCI Express* Interface

PCI Interface

SATA Interface

USB Host Interface

SMBus Host Interface

SPI Interface

LPC interface to IBMC

JTAG interface

LAN interface

ACPI interface

3.4 I/O Sub-system

Intel

®

3420 Chipset PCH provides extensive I/O support.

3.4.1 PCI Express Interface

Two different PCI-E configurations on single board are dependent on different board SKUs:

Intel

®

Server Board S3420GPLX

One PCI-E X16 slot connected to the PCI-E ports of CPU. Two PCI-E x8 slots and one SAS

module connected to PCI-E ports of PCIe switch. One PCI-E X8 slot and one PCI-E x4 slot

connected to the PCI-E ports of PCH.

Intel

®

Server Board S3420GPLC

One PCI-E X16 slot and one PCI-E X8 slot connected to the PCI-E ports of CPU. One PCI-

E x8 slot connected to the PCI-E ports of PCH.

Intel

®

Server Board S3420GPV

One PCI-E X16 slot and one PCI-E X8 slot connected to the PCI-E ports of CPU. One PCI-

E x8 slot connected to the PCI-E ports of PCH.

There is one 32-bit, 33-MHz, 3.3-V/5-V PCI slot.

Compatibility with the PCI addressing model is maintained to ensure all existing applications

and drivers operate unchanged.

The PCI Express* configuration uses standard mechanisms as defined in the PCI Plug-and-

Play specification. The initial recovered clock speed of 1.25 GHz results in 2.5 Gb/s/direction,

which provides a 250-MB/s communications channel in each direction (500 MB/s total). This is

close to twice the data rate of classic PCI. The fact that 8b/10b encoding is used accounts for

the 250 MB/s where quick calculations would imply 300 MB/s. The external graphics ports

support 5.0 GT/s speed as well. Operating at 5.0 GT/s results in twice as much bandwidth per

lane as compared to 2.5 GT/s operation.

When operating with two PCI Express* controllers, each controller can operate at either 2.5

GT/s or 5.0 GT/s. The PCI Express* architecture is specified in three layers: Transaction Layer,

Data Link Layer, and Physical Layer. The partitioning in the component is not necessarily along

these same boundaries.

Loading...

Loading...