Intel® Xeon® Processor E5-2600 Product Family Uncore Performance Monitoring

58 Reference Number: 327043-001

TxR_BL_CYCLES_FULL

• Title: BL Egress Full

• Category: BL_EGRESS Events

• Event Code: 0x36

• Max. Inc/Cyc: 1, Register Restrictions: 0-3

• Definition: BL Egress Full

WPQ_CYCLES_NO_REG_CREDITS

• Title: HA iMC CHN0 WPQ Credits Empty - Regular

• Category: WPQ_CREDITS Events

• Event Code: 0x18

• Max. Inc/Cyc: 4, Register Restrictions: 0-3

• Definition: Counts the number of cycles when there are no "regular" credits available for posting

writes from the HA into the iMC. In order to send writes into the memory controller, the HA must

first acquire a credit for the iMC's WPQ (write pending queue). This queue is broken into regular

credits/buffers that are used by general writes, and "special" requests such as ISOCH writes. This

count only tracks the regular credits Common high banwidth workloads should be able to make use

of all of the regular buffers, but it will be difficult (and uncommon) to make use of both the regular

and special buffers at the same time. One can filter based on the memory controller channel. One

or more channels can be tracked at a given time.

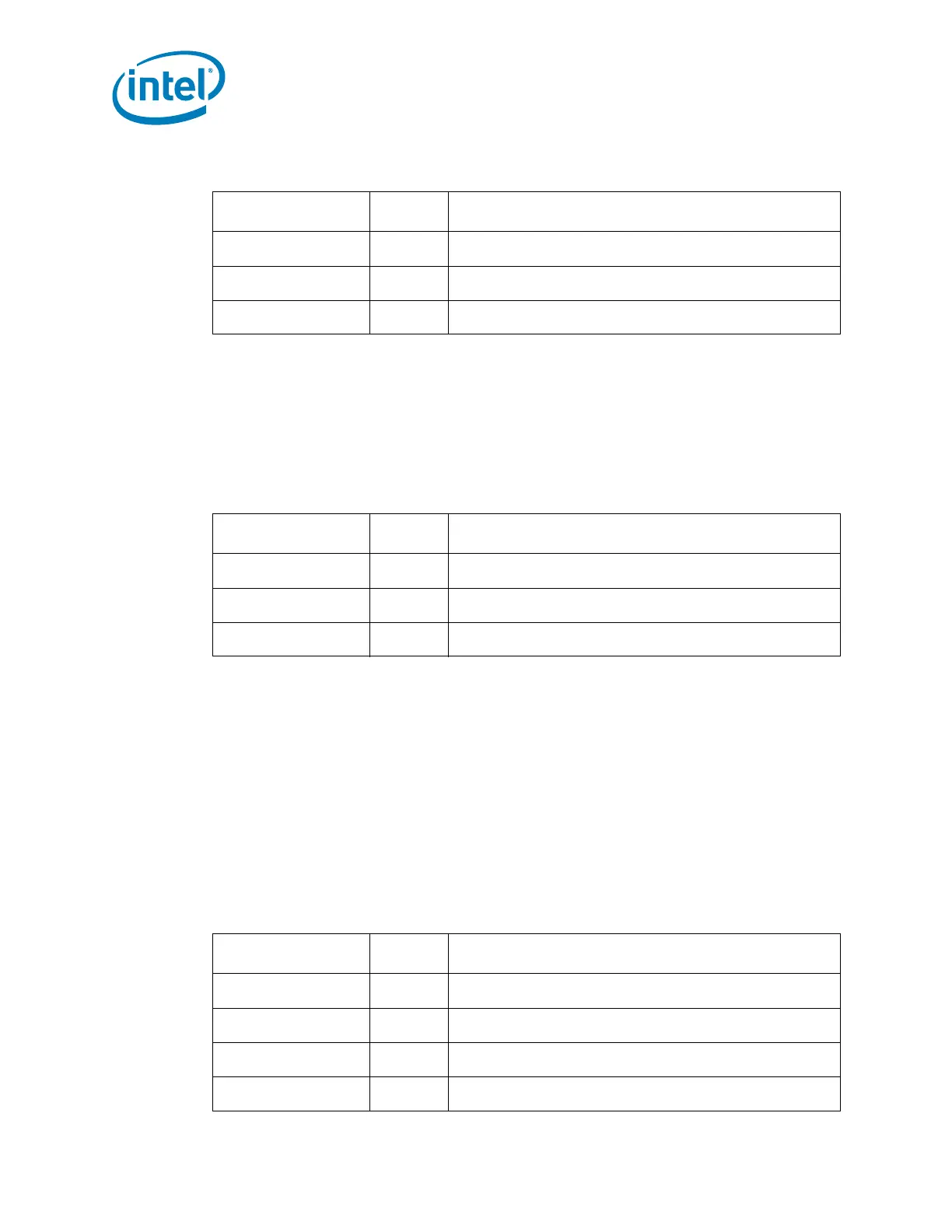

Table 2-56. Unit Masks for TxR_BL

Extension

umask

[15:8]

Description

DRS_CACHE bxxxxxxx1 Data to Cache:

Filter for data being sent to the cache.

DRS_CORE bxxxxxx1x Data to Core:

Filter for data being sent directly to the requesting core.

DRS_QPI bxxxxx1xx Data to Intel® QPI:

Filter for data being sent to a remote socket over Intel® QPI.

Table 2-57. Unit Masks for TxR_BL_CYCLES_FULL

Extension

umask

[15:8]

Description

SCHED0 bxxxxxxx1 Scheduler 0:

Filter for cycles full from scheduler bank 0

SCHED1 bxxxxxx1x Scheduler 1:

Filter for cycles full from scheduler bank 1

ALL bxxxxxx11 All:

Cycles full from both schedulers

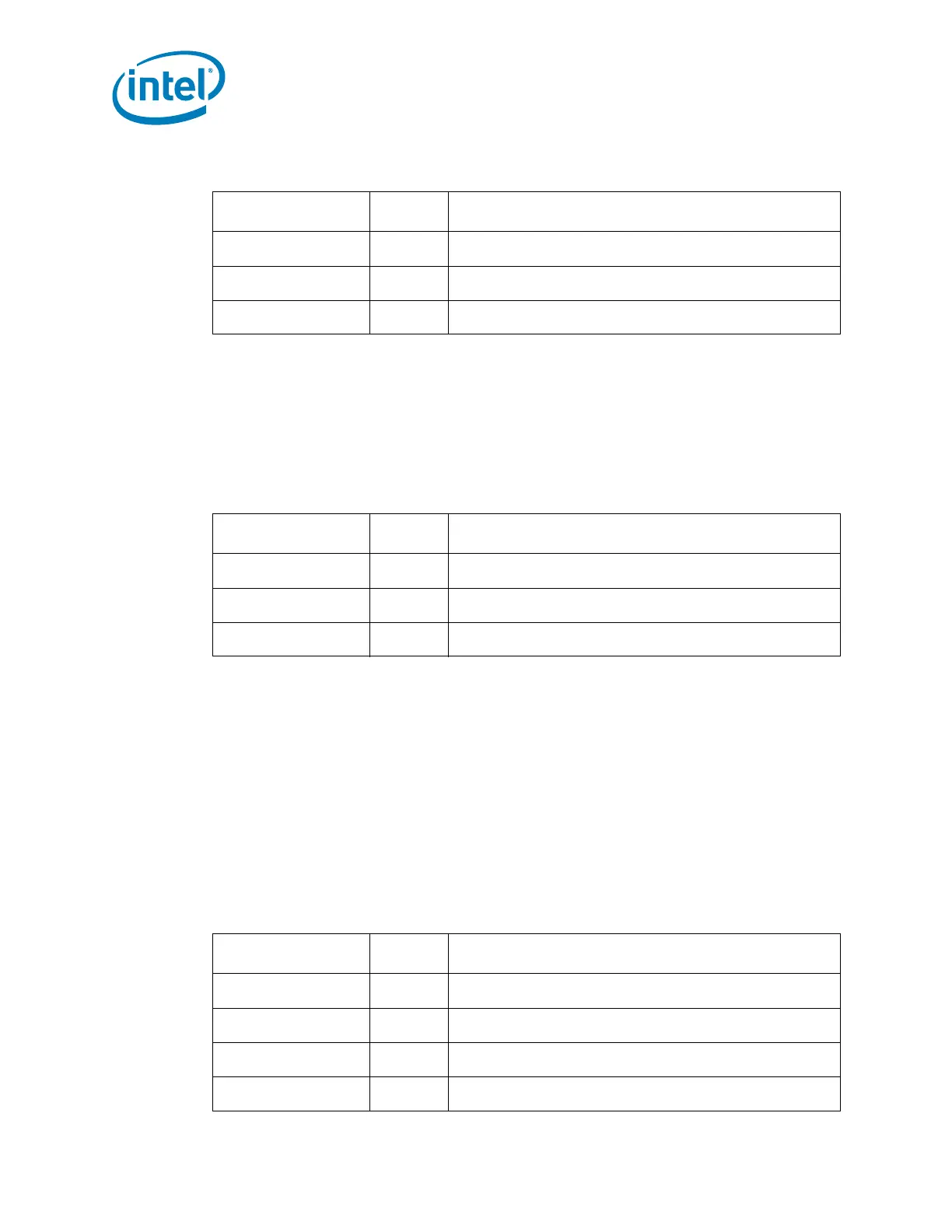

Table 2-58. Unit Masks for WPQ_CYCLES_NO_REG_CREDITS

Extension

umask

[15:8]

Description

CHN0 bxxxxxxx1 Channel 0:

Filter for memory controller channel 0 only.

CHN1 bxxxxxx1x Channel 1:

Filter for memory controller channel 1 only.

CHN2 bxxxxx1xx Channel 2:

Filter for memory controller channel 2 only.

CHN3 bxxxx1xxx Channel 3:

Filter for memory controller channel 3 only.

Loading...

Loading...